# **Springer Theses** Recognizing Outstanding Ph.D. Research

# Felix Winterstein

# Separation Logic for High-level Synthesis

# **Springer Theses**

Recognizing Outstanding Ph.D. Research

#### Aims and Scope

The series "Springer Theses" brings together a selection of the very best Ph.D. theses from around the world and across the physical sciences. Nominated and endorsed by two recognized specialists, each published volume has been selected for its scientific excellence and the high impact of its contents for the pertinent field of research. For greater accessibility to non-specialists, the published versions include an extended introduction, as well as a foreword by the student's supervisor explaining the special relevance of the work for the field. As a whole, the series will provide a valuable resource both for newcomers to the research fields described, and for other scientists seeking detailed background information on special questions. Finally, it provides an accredited documentation of the valuable contributions made by today's younger generation of scientists.

#### Theses are accepted into the series by invited nomination only and must fulfill all of the following criteria

- They must be written in good English.

- The topic should fall within the confines of Chemistry, Physics, Earth Sciences, Engineering and related interdisciplinary fields such as Materials, Nanoscience, Chemical Engineering, Complex Systems and Biophysics.

- The work reported in the thesis must represent a significant scientific advance.

- If the thesis includes previously published material, permission to reproduce this must be gained from the respective copyright holder.

- They must have been examined and passed during the 12 months prior to nomination.

- Each thesis should include a foreword by the supervisor outlining the significance of its content.

- The theses should have a clearly defined structure including an introduction accessible to scientists not expert in that particular field.

More information about this series at http://www.springer.com/series/8790

Felix Winterstein

# Separation Logic for High-level Synthesis

Doctoral Thesis accepted by Imperial College London, UK

Author Dr. Felix Winterstein Department of Electrical and Electronic Engineering Imperial College London London UK Supervisor Prof. George A. Constantinides Imperial College London London UK

ISSN 2190-5053

ISSN 2190-5061 (electronic)

Springer Theses

ISBN 978-3-319-53221-9

ISBN 978-3-319-53222-6 (eBook)

DOI 10.1007/978-3-319-53222-6

ISBN 978-3-319-53222-6 (eBook)

Library of Congress Control Number: 2017930280

#### © Springer International Publishing AG 2017

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Printed on acid-free paper

This Springer imprint is published by Springer Nature The registered company is Springer International Publishing AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland To Stephanie and Leonas and my parents.

### **Supervisor's Foreword**

It gives me great pleasure to introduce this book, based on the work of my former Ph.D. student Felix Winterstein. I have worked in the field of High-Level Synthesis (HLS) for more than 15 years, and it has never been as exciting as it is today. Industry is beginning to adopt HLS as the design flow of choice. As a result, research that once ended up purely as academic papers now finds itself pored over by a variety of industry vendors, all looking to improve their HLS offering. At the same time, the adoption of FPGAs in the datacentre is driving the demand for-and excitement about-FPGA HLS. This book contains the core ideas for a radical extension of the reach of HLS to encompass efficient hardware realisations of a wide variety of algorithms previously out of reach to existing design tools. As with all the best academic research, there is a significant departure from the industrial status quo here, yet Dr. Winterstein has integrated his approach with existing design tools so that the promise of the approach is visible—and accessible—to all. In these pages, you will find a skilful and intelligent blend of mathematical logic, algorithms, digital design and compilers. I hope you enjoy reading this book as much as I enjoyed supervising the work.

November 2016

Prof. George A. Constantinides Imperial College London London UK

#### Abstract

High-level synthesis (HLS) promises a significant shortening of the digital hardware design cycle by raising the abstraction level of the design entry to high-level languages such as C/C++. However, applications using dynamic, pointer-based data structures remain difficult to implement well, yet such constructs are widely used in software. Automated optimisations that leverage the memory bandwidth of dedicated hardware implementations by distributing the application data over separate on-chip memories and parallelise the implementation are often ineffective in the presence of dynamic data structures, due to the lack of an automated analysis that disambiguates pointer-based memory accesses. This thesis takes a step towards closing this gap. We explore recent advances in separation logic, a rigorous mathematical framework that enables formal reasoning about the memory access of heap-manipulating programs. We develop a static analysis that automatically splits heap-allocated data structures into provably disjoint regions. Our algorithm focuses on dynamic data structures accessed in loops and is accompanied by automated source-to-source transformations which enable loop parallelisation and physical memory partitioning by off-the-shelf HLS tools.

We then extend the scope of our technique to pointer-based memory-intensive implementations that require access to an off-chip memory. The extended HLS design aid generates parallel on-chip multi-cache architectures. It uses the disjointness property of memory accesses to support non-overlapping memory regions by private caches. It also identifies regions that are shared after parallelisation and that are supported by parallel caches with a coherency mechanism and synchronisation, resulting in automatically specialised memory systems. We show up to  $15 \times$  acceleration from heap partitioning, parallelisation and the insertion of the custom cache system in demonstrably practical applications.

#### Acknowledgements

I would like to thank my Ph.D. advisor Prof. George Constantinides for his encouragement, for his excellent support and for sparking my interest in separation logic. George has given me the freedom to pursue my own research questions and helped guide my thoughts with sage advice, sharp insight and inspiring ideas. It is largely due to the research environment he has created that this work resulted in a thesis of which I am proud.

I thank my colleagues at Imperial, especially Shane Fleming, Andrea Suardi, John Wickerson, Samuel Bayliss, Michalis Vavouras, Grigorios Mingas, Nadesh Ramanathan, David Boland and Ivan Beretta who have made the Circuits and Systems Group an inspiring and vibrant work environment. Special thanks go to Shane and his wife Iza who have become close friends and regularly hosted me during the many short visits to London.

I also thank the European Space Agency for funding my research and my former colleagues from ESA's Ground Station Systems Division for being such pleasant company. In particular, I would like to thank Gunther Sessler for being an excellent mentor and a friend. In addition to him, it was with the help of Marco Lanucara and Piermario Besso that my application for ESA's contribution to my Ph.D. funding was successful.

Outside of Imperial and ESA, I would like to thank Hsin-Jung Yang from MIT and Elliott Fleming from Intel for a very productive collaboration during the last two years.

I am grateful for the advice and support given by my parents Sabine and Bernhard Winterstein and my brother Florian.

Finally, I thank my wonderful partner Stephanie for her love, patience and support.

You made this thesis possible.

# Contents

| 1 | Intr | oduction                                               | 1  |

|---|------|--------------------------------------------------------|----|

|   | 1.1  | Research Contributions                                 | 5  |

|   | 1.2  | Thesis Outline                                         | 6  |

|   | 1.3  | Statement of Originality                               | 6  |

|   | Refe | rences                                                 | 8  |

| 2 | Higl | n-Level Synthesis of Dynamic Data Structures           | 11 |

|   | 2.1  | Background                                             | 13 |

|   | 2.2  | Analysis of the Filtering Algorithm                    | 17 |

|   | 2.3  | RTL Implementations                                    | 19 |

|   |      | 2.3.1 Lloyd's Algorithm                                | 19 |

|   |      | 2.3.2 Filtering Algorithm                              | 20 |

|   | 2.4  | HLS Implementations                                    | 22 |

|   |      | 2.4.1 Lloyd's Algorithm                                | 23 |

|   |      | 2.4.2 Filtering Algorithm                              | 23 |

|   | 2.5  | Performance Comparison                                 | 26 |

|   |      | 2.5.1 RTL Designs                                      | 26 |

|   |      | 2.5.2 HLS Designs                                      | 28 |

|   | 2.6  | Summary                                                | 30 |

|   | Refe | rences                                                 | 32 |

| 3 | Bac  | kground                                                | 35 |

|   | 3.1  | Profiling and User Annotation-Based Approaches         | 36 |

|   | 3.2  | Automated Static Analyses for Static Control Parts     | 37 |

|   | 3.3  | Limitations and Extensions of the Polyhedral Framework | 40 |

|   | 3.4  | HLS Support for Pointers and Dynamic Memory Allocation | 41 |

|   | 3.5  | Static Analysis Based on Separation Logic              | 43 |

|   |      | 3.5.1 Modelling Program State in Separation Logic.     | 44 |

|   |      | 3.5.2 Programming Language                             | 46 |

|   |      | 3.5.3 Symbolic Execution of Programs                   | 47 |

|   |      | 3.5.4   | Theorem Proving                                    | 49  |

|---|------|---------|----------------------------------------------------|-----|

|   |      | 3.5.5   | Application to HLS                                 | 52  |

|   | Refe | erences |                                                    | 52  |

| 4 | Hea  | p Parti | tioning and Parallelisation                        | 57  |

|   | 4.1  |         | ating Example                                      | 59  |

|   | 4.2  |         | m Analysis                                         | 62  |

|   |      | 4.2.1   | Inserting Cut-Points                               | 63  |

|   |      | 4.2.2   | Proving Communication-Free Parallelism             | 65  |

|   |      | 4.2.3   | Assigning Heap Partition Information to Statements | 67  |

|   | 4.3  | Implei  | mentation.                                         | 69  |

|   |      | 4.3.1   | Heap Analyser                                      | 69  |

|   |      | 4.3.2   | Memory Access                                      | 70  |

|   |      | 4.3.3   | Dynamic Memory Allocation                          | 71  |

|   |      | 4.3.4   | Control and Data Flow                              | 71  |

|   |      | 4.3.5   | Source-to-Source Compiler                          | 72  |

|   | 4.4  |         | iments                                             | 74  |

|   | 4.5  | -       | mance and Robustness of the Heap Analysis          | 80  |

|   | 4.6  |         | $\operatorname{ary}$                               | 83  |

|   |      |         |                                                    | 84  |

| _ |      |         |                                                    |     |

| 5 |      |         | ulti-cache Architectures                           | 85  |

|   | 5.1  |         | ating Example                                      | 87  |

|   |      | 5.1.1   | Memory Partitioning and Parallelisation            | 89  |

|   |      | 5.1.2   | Parallel Access to Shared Resources                | 90  |

|   |      | 5.1.3   | Custom Cache Sizing                                | 91  |

|   | 5.2  |         | ded Static Program Analysis                        | 92  |

|   |      | 5.2.1   | Detecting Private and Shared Resources             | 94  |

|   |      | 5.2.2   | Commutativity Analysis                             | 95  |

|   | 5.3  |         | Generation                                         | 97  |

|   | 5.4  |         | m Cache Sizing                                     | 99  |

|   |      | 5.4.1   | On-Chip Memory Utilisation Estimation              | 101 |

|   |      | 5.4.2   | Cache Performance Estimation                       | 102 |

|   |      | 5.4.3   | Optimisation Strategy                              | 104 |

|   | 5.5  | Experi  | iments                                             | 104 |

|   |      | 5.5.1   | Hybrid Multi-cache Architectures                   | 105 |

|   |      | 5.5.2   | Validating the BRAM Estimation for Automated       |     |

|   |      |         | Cache Scaling                                      | 108 |

|   |      | 5.5.3   | Validating Cache Performance Estimation            | 108 |

|   |      | 5.5.4   | Latency and Resource Utilisation After Custom      |     |

|   |      |         | Cache Scaling                                      | 109 |

|   |      | 5.5.5   | Energy Consumption                                 | 112 |

|   | 5.6  | Summ    | ary                                                | 113 |

|   | Refe | erences |                                                    | 114 |

| 6  | Con  | clusion                           | 117 |

|----|------|-----------------------------------|-----|

|    | 6.1  | Outlook                           | 120 |

|    | 6.2  | Final Remarks                     | 122 |

|    | Refe | rences                            | 122 |

| Ap | pend | ix A: Context-Aware Heap Analysis | 125 |

# List of Figures

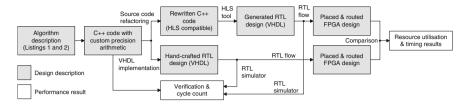

| Figure 2.1 | Design flow of the case study                                | 13 |

|------------|--------------------------------------------------------------|----|

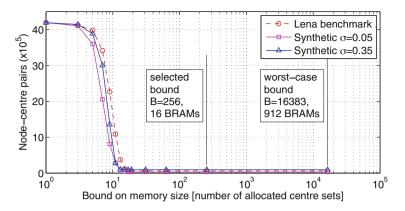

| Figure 2.2 | Left Frequency of candidate centre set sizes for synthetic   |    |

| -          | input data. Right Computational complexity of the filtering  |    |

|            | algorithm in terms of node-centre pairs                      |    |

|            | (Lloyd's algorithm has a constant complexity                 |    |

|            | of $209.7 \times 10^4$ point-centre pairs for this data set) | 18 |

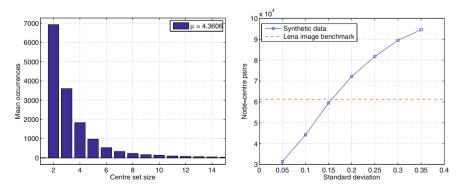

| Figure 2.3 | Left FPGA implementation of the filtering algorithm.         |    |

|            | Right Read-write accesses to the scratchpad memory           |    |

|            | for centre sets during tree traversal                        | 20 |

| Figure 2.4 | Trade-off between heap size and run-time                     |    |

| -          | of the filtering algorithm (profiling)                       | 22 |

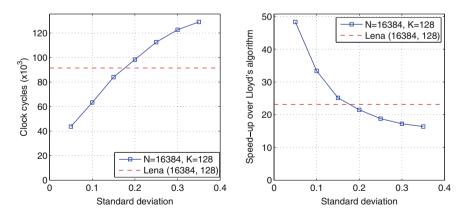

| Figure 2.5 | Left Average cycle count per iteration for the manual        |    |

|            | RTL implementation of the filtering algorithm $(P = 1)$ .    |    |

|            | Right Speed-up over an RTL implementation                    |    |

|            | of Lloyd's algorithm ( $P = 1$ in both cases)                | 26 |

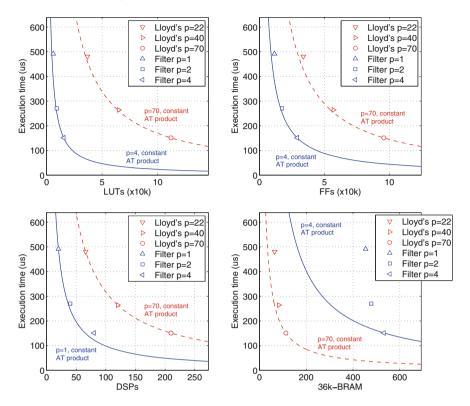

| Figure 2.6 | Mean execution time per iteration over FPGA                  |    |

|            | resources for $N = 16384, K = 128, \sigma = 0.2$             |    |

|            | (Xilinx Virtex7 7vx485tffg-2)                                | 27 |

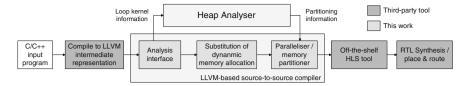

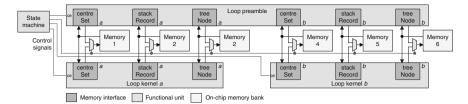

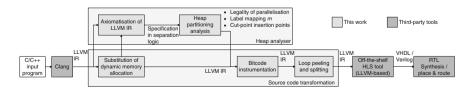

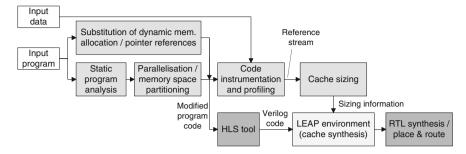

| Figure 4.1 | High-level compilation tool flow                             | 58 |

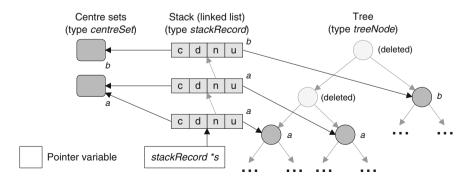

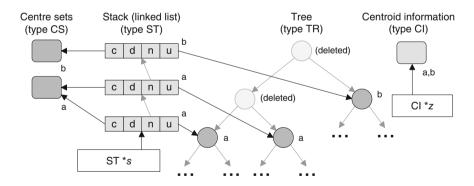

| Figure 4.2 | Snapshot of the linked data structures accessed              |    |

|            | by the loop in Listing 4.1                                   | 60 |

| Figure 4.3 | Synthesised hardware from the transformed code               |    |

|            | in Listing 4.2                                               | 61 |

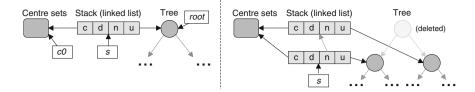

| Figure 4.4 | Pre-state before execution of the first ( <i>left</i> )      |    |

|            | and the second loop iteration (right)                        | 64 |

| Figure 4.5 | LLVM-based CAD flow including the heap analyser,             |    |

|            | source translator and third party tools for HLS              |    |

|            | and RTL implementation                                       | 69 |

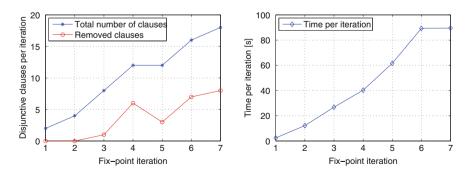

| Figure 4.6 | Analysis complexity for Filter. Left number of disjunctive   |    |

|            | clauses (total and removed). Right tool execution time       |    |

|            | per fix-point iteration                                      | 80 |

| Figure 4.7 | Punctured linked list                                      | 81  |

|------------|------------------------------------------------------------|-----|

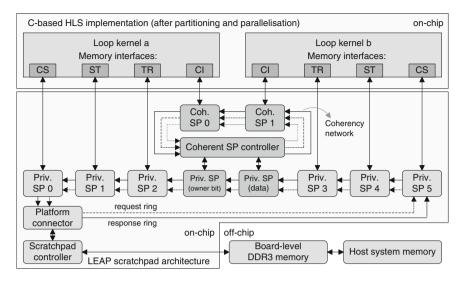

| Figure 5.1 | Summary of the extended tool flow presented                |     |

|            | in this chapter                                            | 86  |

| Figure 5.2 | Snapshot of the pointer-linked dynamic data structures     |     |

|            | accessed by the loop in Listing 5.1                        | 89  |

| Figure 5.3 | Parallelised HLS implementation of the filtering algorithm |     |

|            | with a hybrid cache architecture                           | 98  |

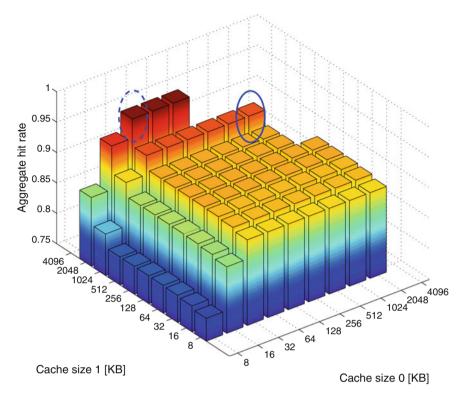

| Figure 5.4 | Aggregate hit rate estimate for a two-cache system         |     |

|            | with an 2200 kB on-chip memory constraint                  | 101 |

| Figure A.1 | Heap layout and pointer assignment during the first four   |     |

|            | iterations of the loop in Listing A.1                      | 126 |

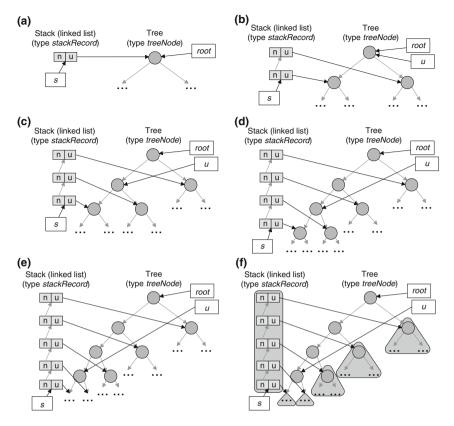

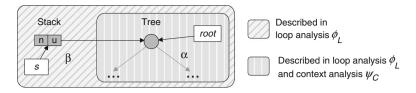

| Figure A.2 | Program state described by the two sub-analyses $\phi_L$   |     |

|            | and $\psi_C$ in (A.4)                                      | 129 |

|            |                                                            |     |

## List of Tables

| Table 2.1 | Computational complexity of the filtering algorithm         |     |

|-----------|-------------------------------------------------------------|-----|

|           | broken down into clustering and pre-processing phases       | 18  |

| Table 2.2 | Resource comparison for a 270 µs-latency constraint         |     |

|           | (input parameters: $N = 16,384, K = 128, \sigma = 0.2$ )    | 28  |

| Table 2.3 | Performance comparison using the hand-written RTL           |     |

|           | designs as reference                                        | 29  |

| Table 4.1 | Implementation results and comparison                       | 76  |

| Table 4.2 | Comparison with hand-written HLS/RTL designs                | 79  |

| Table 4.3 | Tool execution time                                         | 80  |

| Table 5.1 | Parallelisation and caching (cache size 1 kB)               | 106 |

| Table 5.2 | Cost increase of all-coherent default compared to           |     |

|           | application-specific hybrid scratchpad architectures        | 107 |

| Table 5.3 | High-level BRAM estimation accuracy                         |     |

|           | (results in 36k-RAM blocks)                                 | 109 |

| Table 5.4 | Cache hit/miss count estimation for two private             |     |

|           | caches in <b>Reflect tree</b>                               | 110 |

| Table 5.5 | Latency and resource utilisation after custom cache scaling | 111 |

| Table 5.6 | Power and energy measurements                               | 112 |

## Chapter 1 Introduction

With the increasing demand for performance and efficiency of computing devices, *custom computing* is a growing area in digital computation today, which represents a class of processing devices that are dedicated to an application or a range of similar applications. Custom computing devices can achieve higher energy or power efficiency and performance with respect to general-purpose microprocessors, which can execute any task on the same underlying hardware [1–9]. Efficiency and performance are gained by avoiding unnecessary circuitry for a specific computing task, and the design of custom data paths and memory systems. The trade-off between flexibility and performance/efficiency varies across different classes of specialised computing machines: Digital signal processors and application-specific instruction set processors (ASIPs) are software-programmable and provide extended hardware support for domain-specific features. On the other hand, digital application-specific integrated circuits (ASICs) are fully customised processors that implement computation based on a digital circuit which is usually dedicated to a single application; once produced, the functionality of an ASIC is hard-wired and cannot be changed. Field-programmable gate arrays (FPGAs) have a particular role in the flexibility/performance trade-off in that they combine programmability with an efficient dedicated circuit implementation for a particular application. An FPGA consists of configurable logic cells and interconnects and typically can be reprogrammed to implement different computing tasks post-fabrication.

The traditional design entries of ASIC and FPGA implementations are largely similar in the first phases of the design flow. A hardware model is written in a hardware description language (HDL) such as VHDL [10] or Verilog [11] at the level of abstraction referred to as register transfer level (RTL). The specification at RTL allows the user to have full control over the low-level details of the data path and memory system implementations on the chip and to navigate the implementation through a large design space. However, producing a manual RTL specification requires significant design and verification effort, including several iterations of design optimisation and verification phases. The development times for complex ASIC implementations may amount to several years until tape-out, while RTL design and verification dominate the overall development cycle. The design cycle for FPGA implementations is

<sup>©</sup> Springer International Publishing AG 2017

F. Winterstein, *Separation Logic for High-level Synthesis*, Springer Thesis, DOI 10.1007/978-3-319-53222-6\_1

typically shorter, but the design effort at RTL is similar. Long implementation cycles are a hindrance for an adoption of FPGAs as efficient yet flexible processing devices: reprogrammability encourages their use in a similar way as microprocessors are used in that the same hardware can execute different 'programs'. However, prohibitively long development times compared to software implementations fundamentally limit this versatility. Furthermore, the RTL design entry inevitably requires familiarity with the low-level details of digital hardware design. The conceptual difference between the application development for FPGAs and for instruction set architectures hinders the wide adoption of FPGA technology by software developers and application engineers without experience in circuit design [12].

The low productivity of application development at RTL has encouraged the electronic design automation (EDA) community to raise the abstraction level of application descriptions from RTL to high-level languages such as C/C++. High-level synthesis (HLS) tools take these descriptions as input and automatically generate RTL specifications which can be synthesised and mapped into hardware by standard backend RTL tool flows. High-level design entry can significantly shorten the development cycle when compared with RTL-based specification. Remarkable effort in academia and industry has led to various HLS tools targeting ASIC and FPGA technology. With C/C++ being one of the most prevalent programming languages used to date and with large bases of legacy codes written in it, RTL compilation from C/C++ and derivatives thereof has a long-standing tradition in industrial [13–22] and academic [23–27] development. The admissible source code entry to these tools is restricted to synthesisable subsets of the C language.

HLS has experienced an increased interest in the last decade, which we believe is due to two main reasons. Firstly, state-of-the-art tools have increased performance compared to previous generations of tools developed in the mid 1990s [28]. The performance of an HLS tool can be measured in the quality of results (QoR) of the resulting RTL description in terms of execution time and hardware resource utilisation. Recent evaluations [29–31] show that state-of-the-art tools, such as Xil-inx Vivado HLS [20], can achieve a QoR comparable to hand-written HDL code. Secondly, technology scaling has brought the number of transistors on a chip to point where the RTL design effort required to make efficient use this resource is becoming an increasingly severe limitation [12]. On the other hand, the abundance of hardware resources makes the trade-off between the QoR of hand-written HDL and generated HLS designs and design times appealing to more and more users, a fact that is especially true for FPGA implementations whose end-to-end development time is usually significantly shorter than that of ASIC designs [12, 32].

Despite the encouraging QoR results of FPGA-targeted HLS evaluations for particular benchmarks [29–33], there are types of programs that either cannot be synthesised at all, or result in a poor QoR. Applications using dynamic, pointer-based data structures and dynamic memory allocation are examples of such programs. The objective of this thesis is to extend the scope of current HLS to such *pointer-based* programs. Our work is motivated by the fact that pointer-based memory references and dynamic memory allocation are well established and widely used features of high-level languages such as C++. However, their analysis and automated program optimisations resulting from it are beyond the scope of the overwhelming majority of HLS techniques to date. Although dynamic memory allocation, an unsupported feature in common HLS flows, can be made synthesisable with manual source code modifications, pointer-based programs often do not result in efficient hardware implementations. As we shall see in Chap. 2, the HLS implementation of such a program can be degraded by a factor larger than  $26 \times$  in terms of execution time compared to a hand-crafted RTL design if the source code is not further optimised prior to HLS. The reward for extensive manual code optimisations is shown to be an  $8 \times$  improvement of the execution time.

We identify two aspects that are crucial for improving the QoR. The first is the extraction of parallelism from a pointer-based application while preserving the program semantics, which is usually based on a dependence analysis. Secondly, computational parallelism requires that the memory system is not a sequential bottleneck to performance. We aim to make efficient use of the customisable memory architecture in FPGAs, which is a key feature distinguishing FPGAs from microprocessors. Instead of a monolithic memory space, the application data can be distributed over many small blocks of on-chip memory leading to a high aggregate memory bandwidth. Consequently, multiple computational units can be fed in parallel which results in a very efficient parallelisation if expensive dynamic interconnects between any memory and any worker in a parallel computational unit can be reduced to single peer-to-peer connections, i.e. the parallelism is communication-free. The C model, however, assumes the presence of a *heap*, a large monolithic memory space in which a program allocates and frees up portions at run time. The difficulty of parallelisation and memory partitioning lies in the disambiguation of memory references: regardless of scope, every two heap-directed pointers potentially alias, i.e. reference the same memory cell, which leads to dependencies between expressions that are syntactically unrelated. The difficulty of analysing these programs is exacerbated by linked data structures which contain pointers in their link fields.

Expanding on the encouraging results in Chap. 2, the scope of this thesis is to automate source code transformations that enable parallelisation and memory partitioning in HLS flows. We present a static program analysis which breaks the monolithic heap memory into several disjoint portions, which we refer to as *heaplets* in this thesis, and rules out dependencies between code fragments that a standard HLS tool must assume potentially exist. The dependence/disjointness analysis enables automated source-to-source transformations for parallelisation and data distribution which can be exploited by a back-end HLS tool. Our departure point from previous work is the use of recent advances in *separation logic* [34], a mathematical framework that allows a rigorous formal description of the program state and reasoning about the resources accessed by a program. Separation logic extends the classical propositional logic by an operator that explicitly expresses the separation of resources, i.e. the non-aliasing property of two pointers. This paves the way for an automated program analysis and can straightforwardly handle dynamic memory allocation in disjoint heaplets. Separation logic has predominantly been leveraged in modern software verification tools. To the best of our knowledge, its application in the context of automated code optimisations for HLS remains largely unexplored. Experiments in Chap. 4, comparing

the automatically parallelised to the direct HLS implementations, show an average reduction of execution time by a factor of  $2.4 \times$  across several benchmarks.

Besides the on-chip memory partitioning and parallelisation, our source-to-source transformations ensure the synthesisability of heap-manipulating programs including dynamic memory allocation by standard HLS tools. The implementations in Chap. 4 are constructed under the assumption that the application data fits in the physical onchip memory. However, the chances of exhausting the memory resources in an FPGA application with a large memory footprint are high since the maximum capacity of on-chip memory in state-of-the-art FPGAs is only in the order of tens of megabytes. We remove the limitation of being restricted to on-chip memory implementations in Chap. 5 by embedding HLS kernels in a framework that provides access to an external memory hierarchy consisting of board-level dynamic random access memory (DRAM) and host machine-level main memory. Accessing external memory, however, can substantially slow down the FPGA accelerator due to memory bandwidth limitations and, in the worst case, the contention on the external memory bus eliminates the gain of parallelisation. The starting point for our work in Chap. 5 is the insertion of on-chip caches to buffer frequently reused data and to reduce the number of expensive accesses to the external memory.

Our main contribution in Chap. 5 is the application of an extended version of the baseline analysis in Chap. 4 to the automatic generation of an application-specific on-chip multi-cache architecture. Firstly, we extend the analysis such that, at compile time, it provides precise information about which regions in heap memory will be shared after the implementation has been parallelised. This extends its scope to programs whose memory access pattern does not allow a partitioning into fully independent computational units and therefore broadens the applicability of our technique. Secondly, we use the disjointness/sharing information to instantiate an applicationspecific, hybrid multi-cache system that contains *private* caches for heap regions known to be private for a computational unit and caches with an additional (and inherently more expensive) coherence mechanism and synchronisation service for shared heap regions. In the remainder of this thesis, we distinguish between these two modes by referring to private and coherent caches, while the latter case corresponds to inter-cache coherency. We also extend the multi-cache construction with a technique for custom sizing so as to maximise the aggregate hit rate in private caches under a memory resource constraint. We demonstrate a speed-up of up to  $15.2 \times$  after parallelisation and generation of a multi-cache architecture compared to the unparallelised application and uncached access to the off-chip memory. Furthermore, the hybrid system outperforms a default all-coherent version by 69.3% on average in terms of the area-time product across our benchmarks.

This thesis moves us towards the goal of supporting full-featured C/C++ code in future HLS flows by providing a framework that enables efficient FPGA acceleration of irregular computation over pointer-based data structures. In Sect. 4.3, we propose an approach to integrate this framework into future HLS tools. The overall vision is that 'standard' software codes, including those from legacy code bases which have not been developed with HLS in mind, can be equally seamlessly mapped to FPGA

accelerators while leaving the platform-specific optimisations to the compiler. This further raises the level of abstraction in digital hardware design and may lead to a wider adoption of FPGA technology in an extended scope of applications.

#### **1.1 Research Contributions**

This thesis makes the following main contributions:

- A separation logic-based parallelisation algorithm for pointer-based programs which access dynamic data structures. Our static program analysis handles straightline code as well as arbitrary while-loops and determines whether communication-free parallelism can be exposed in the loop execution with respect to the accessed dynamic data structures. Starting from the C memory model of a global monolithic heap memory, it determines how to partition the heap and dynamic data structures into disjoint partitions that can be implemented in separate on-chip memory blocks.

- The implementation of an automated source-to-source transformation infrastructure: The source translator ensures synthesisability of code containing unsupported constructs related to dynamic memory allocation. In a second pass, the disjointness information provided by our analysis is used to split the synthesised heap memory into separate blocks and to split a loop into multiple loops so as to obtain a semantically equivalent parallel implementation. The property of communication-free parallelism ensures that each functional unit only requires access to its own private memory block.

- In addition to the identification of disjoint heap regions, we extend the baseline heap analysis by an identification of heaplets that would be shared by the parallel loop kernels after parallelisation. Our analysis inserts additional synchronisation primitives for program fragments that access shared resources. Even if coherency is ensured, updates to the shared resource may happen in a different order after parallelisation compared to the sequential program. We present a *commutativity analysis* for the shared heap update in order to prove that the parallelisation is semantics-preserving.

- The extended framework targets FPGA accelerators with access to an off-chip memory. The disjointness and sharing information provided by our analyses are used to break the heap (residing in off-chip memory by default) into heaplets, to generate an application-specific parallel multi-scratchpad architecture containing on-chip caches and (if needed) coherency mechanisms: we synthesise parallel private scratchpads for disjoint heap regions and (inherently more expensive) coherent parallel scratchpads for shared regions.

- We further extend this framework by automated size scaling of private on-chip caches that uses spare on-chip memory resources. We generate individual sizing information for the multi-cache system and find the best size distribution for a user-provided memory access pattern of a particular application.

#### 1.2 Thesis Outline

Before discussing the background and related work on program analyses, parallelisation and memory system optimisations in an HLS context in Chap. 3, this thesis begins with the presentation of a case study in the next chapter. The case study compares RTL and HLS implementations of two alternative algorithms for the same compute-intensive machine learning application (clustering) with significantly different computational properties: a data-flow centric implementation and a recursive tree traversal implementation that incorporates data-dependent control flow and makes use of pointer-linked data structures and dynamic memory allocation. The reason for this order of Chaps. 2 and 3 is two-fold: (1) It introduces the type of problems this work addresses and provides a motivating example for mapping an efficient pointerbased algorithm to an FPGA rather than its pointer-less brute-force counterpart. (2) It shows the capabilities and limitations of an exemplary state-of-the-art C-to-FPGA tool when synthesising pointer-based programs and proposes a set of manual source code alterations that result in a significantly more efficient HLS design.

Chapter 3, after the discussion of related work, introduces separation logic, the theoretical framework that provides the foundation of our program analyses in Chaps. 4 and 5. The analysis in Chap. 4 automates an important part of the code transformations of Chap. 2 that enables memory partitioning and parallelisation. Chapter 5 extends the scope of this work to the construction of multi-cache systems and shared memory accesses. Chapter 6 concludes this thesis and summarises the key ideas and concepts developed in this work. It also outlines directions of future research that build on the research contributions made in this thesis.

#### **1.3 Statement of Originality**

This thesis is my own work and all related work is appropriately referenced. The original contributions made in this thesis have been published in the following peer-reviewed conference papers and journal articles:

- F. Winterstein, S. Bayliss and G.A. Constantinides, "Separation Logic for High-Level Synthesis," *ACM Transactions on Reconfigurable Technology and Systems* (*TRETS*), vol. 9, no. 2, pp. 10:1–10:23, Dec. 2015 [35].

- F. Winterstein, K. Fleming, H.-J. Yang, J. Wickerson, G. Constantinides, "Custom-Sized Caches in Application-Specific Memory Hierarchies," *Proceedings of the IEEE International Conference on Field-Programmable Technology (ICFPT)*, pp. 144–151, 2015 [36].

- F. Winterstein, K. Fleming, H.-J. Yang, S. Bayliss, G. Constantinides, "MATCHUP: Memory Abstractions for Heap Manipulating Programs," *Proceedings of the ACM/SIGDA International Symposium on Field-Programmable Gate Arrays (FPGA)*, pp. 136–145, 2015 [37].

- F. Winterstein, S. Bayliss, G. Constantinides: "Separation Logic-Assisted Code Transformations for Efficient High-Level Synthesis," *Proceedings of the IEEE International Symposium on Field-Programmable Custom Computing Machines* (FCCM), pp. 1–8, 2014 (best paper nominee) [38].

- F. Winterstein, S. Bayliss, G. Constantinides: "High-Level Synthesis of Dynamic Data Structures: A Case Study Using Vivado HLS," *Proceedings of the IEEE International Conference on Field-Programmable Technology (ICFPT)*, pp. 362– 365, 2013 [31].

- F. Winterstein, S. Bayliss, G. Constantinides: "FPGA-based K-means Clustering Using Tree-Based Data Structures," *Proceedings of the International Conference* on Field Programmable Logic and Applications (FPL), pp. 1–6, 2013 [39].

The C-based HLS and RTL source code developed for the case study in Chap. 2 were made publicly available in an open source repository<sup>1</sup> [40].

Our work on cache architecture specialisation uses the open-source LEAP (Latency-insensitive Environment for Application Programming) framework [41] to embed the C/C++-based HLS kernels in an environment that constructs on-chip caches and an interface to external DRAM and host system main memory. LEAP is developed jointly at the Massachusetts Institute of Technology (MIT, Computer Science and Artificial Intelligence Laboratory) and the Intel Software and Services Group. The work in Chap. 5 and the corresponding publications [35, 37] were done in collaboration with the LEAP developers Kermin Elliott Fleming from Intel and Hsin-Jung Yang from MIT. Their main contribution was support for integrating our HLS kernels in the LEAP environment. Furthermore, following discussions about automatic cache scaling (also presented in Chap. 5), they implemented a new cache micro-architecture in LEAP that uses buffered banks of on-chip memory to support higher clock rates in large caches, an implementation that is used by our technique. In turn, our HLS benchmarks have been used to support the cache architecture design space explorations, which has led to my co-authorship in the following joint publications:

- H.-J. Yang, K. Fleming, M. Adler, F. Winterstein, J. Emer, "LMC: Automatic Resource-Aware Program-Optimized Memory Partitioning," *Proceedings of the ACM/SIGDA International Symposium on Field-Programmable Gate Arrays* (FPGA), pp. 128–137, 2016 [42].

- H.-J. Yang, K. Fleming, M. Adler, F. Winterstein, J. Emer, "Scavenger: Automating the Construction of Application-Optimized Memory Hierarchies," *Proceedings of the IEEE International Conference on Field Programmable Logic and Applications (FPL)*, pp. 1–8, 2015 [43].

The collaboration with Intel/MIT also resulted in a tutorial session jointly held at the International Conference on Field Programmable Logic and Applications (FPL) in 2015 [44]. Some of the HLS, RTL and Bluespec System Verilog source code

<sup>&</sup>lt;sup>1</sup>https://github.com/FelixWinterstein/Vivado-KMeans.

developed within the scope of Chap. 5 was also made publicly available in an open source repository<sup>2</sup> [45].

Finally, the RTL and HLS implementations developed in the scope of Chap. 2 have been included in other research projects (a case study for dynamic load balancing on FPGAs, fault mitigation in an FPGA-based space processor, and a hardware compiler for higher order functional programs). My contribution to these projects resulted in a co-authorship of the following publications:

- N. Ramanathan, J. Wickerson, F. Winterstein, G.A. Constantinides, "A Case for Work-stealing on FPGAs with OpenCL Atomics," *Proceedings of the ACM/ SIGDA International Symposium on Field-Programmable Gate Arrays (FPGA)*, pp. 48–53, 2016 [46].

- S.T. Fleming, D.B. Thomas, F. Winterstein, FPGAs and Parallel Architectures for Aerospace Applications: Soft Errors and Fault-Tolerant Design. Springer International Publishing, 2016, ch. "A Power-Aware Adaptive FDIR Framework Using Heterogeneous System-on-Chip Modules", pp. 75–90 [47].

- E.A. Pelaez, S. Bayliss, A. Smith, F. Winterstein, D.R. Ghica, D. Thomas, G.A. Constantinides: "Compiling Higher Order Functional Programs to Composable Digital Hardware," *Proceedings of the IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM)*, pp. 234–234, 2014 [48].

#### References

- J. Fowers, G. Brown, P. Cooke, G. Stitt, A performance and energy comparison of fpgas, gpus, and multicores for sliding-window applications," in *Proceedings of the ACM/SIGDA International Symposium on Field Programmable Gate Arrays (FPGA)* (2012), pp. 47–56

- 2. B. Cope, P.Y.K. Cheung, W. Luk, L. Howes, Performance comparison of graphics processors to reconfigurable logic: a case study. IEEE Trans. Comput. **59**(4), 433–448 (2010)

- A. Putnam, A. Caulfield, E. Chung, D. Chiou, K. Constantinides, J. Demme, H. Esmaeilzadeh, J. Fowers, G. Gopal, J. Gray, M. Haselman, S. Hauck, S. Heil, A. Hormati, J.-Y. Kim, S. Lanka, J. Larus, E. Peterson, S. Pope, A. Smith, J. Thong, P. Xiao, D. Burger, A reconfigurable fabric for accelerating large-scale datacenter services, in *Proceedings of the ACM/IEEE International Symposium on Computer Architecture (ISCA)* (2014), pp. 13–24

- Z.K. Baker, M.B. Gokhale, J.L. Tripp, Matched Filter Computation on FPGA, Cell and GPU, in Proceedings of the IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM) (2007), pp. 207–218

- H. Riebler, T. Kenter, C. Plessl, C. Sorge, Reconstructing AES key schedules from decayed memory with FPGAs, in *Proceedings of the IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM)* (2014), pp. 222–229

- J. Chase, B. Nelson, J. Bodily, Z. Wei, D.J. Lee, Real-time optical flow calculations on FPGA and GPU architectures: a comparison study, in *Proceedings of the IEEE International Sympo*sium on Field-Programmable Custom Computing Machines (FCCM) (2008), pp. 173–182

- S. Asano, T. Maruyama, Y. Yamaguchi, Performance comparison of FPGA, GPU and CPU in image processing, in *Proceedings of the International Conference on Field Programmable Logic and Applications (FPL)* (2009), pp. 126–131

<sup>&</sup>lt;sup>2</sup>https://github.com/FelixWinterstein/LEAP-HLS.

- H. Park, S. Vijayvargiya, A. DeHon, Energy minimization in the time-space continuum, in *Proceedings of the International Conference on Field Programmable Technology (ICFPT)* (2015), pp. 64–71

- J. Qiu, J. Wang, S. Yao, K. Guo, B. Li, E. Zhou, J. Yu, T. Tang, N. Xu, S. Song, Y. Wang, H. Yang, Going deeper with embedded FPGA platform for convolutional neural network, in *Proceedings of the 2016 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays* (2016), pp. 26–35

- IEEE Standard VHDL Language Reference Manual, IEEE Std 1076-2008 (Revision of IEEE Std 1076-2002) (2009), pp. 1–626

- IEEE Standard for Verilog Hardware Description Language, IEEE Std 1364-2005 (Revision of IEEE Std 1364-2001) (2006), pp. 1–560

- 12. D. Bacon, R. Rabbah, S. Shukla, FPGA programming for the masses. Queue **11**(2), 40:40–40:52 (2013)

- 13. Y Explorations Excite, Accessed 01 Mar 2016. http://www.yxi.com/products.php

- Calypto Catapult Synthesis, Accessed 19 Dec 2015. http://calypto.com/en/products/catapult/ overview/

- Cadence C-to-Silicon Compiler, Accessed 23 Dec 2015. http://www.cadence.com/products/ sd/silicon\_compiler/

- Cadence Cynthesizer Solution, Accessed 23 Dec 2015. http://www.cadence.com/products/sd/ cynthesizer/

- Cadence Stratus High-Level Synthesis, Accessed 22 Dec 2015. http://www.cadence.com/ products/sd/stratus/

- Impulse CoDeveloper, Accessed 25 Nov 2015. http://www.impulseaccelerated.com/products. htm

- Synopsys Synphony C Compiler, Accessed 26 Nov 2015. https://www.synopsys.com/Tools/ Implementation/RTLSynthesis/Pages/SynphonyC-Compiler.aspx

- 20. Xilinx Vivado HLS, Accessed 12 May 2015. http://www.xilinx.com/products/design-tools/ vivado/integration/esl-design.html

- 21. Altera SDK for OpenCL, Accessed 13 Jan 2016. https://www.altera.com/products/designsoftware/embedded-software-developers/opencl/overview.html

- 22. Xilinx SDAccel Development Environment for OpenCL, Accessed 13 Jan 2016. http://www. xilinx.com/products/design-tools/software-zone/sdaccel.html

- 23. High-Level Synthesis with LegUp, Accessed 20 Oct 2015. http://legup.eecg.utoronto.ca/

- C. Pilato, F. Ferrandi, Bambu: a modular framework for the high level synthesis of memoryintensive applications, in *Proceedings International Conference on Field Programmable Logic* and Applications (FPL) (2013), pp. 1–4

- ROCCC 2.0|Jacquard Computing, Accessed 12 May 2015. http://www.jacquardcomputing. com/roccc/

- R. Nane, V. M. Sima, B. Olivier, R. Meeuws, Y. Yankova, K. Bertels, DWARV 2.0: A CoSybased C-to-VHDL hardware compiler, in *Proceedings of the International Conference on Field Programmable Logic and Applications (FPL)* (2012), pp. 619–622

- GAUT High-Level Synthesis Tool From C to RTL, Accessed 21 Mar 2015. http://hls-labsticc. univ-ubs.fr/

- G. Martin, G. Smith, High-level synthesis: past, present, and future. IEEE Des. Test Comput. 26(4), 18–25 (2009)

- 29. W. Meeus, K. Van Beeck, T. Goedemé, J. Meel, D. Stroobandt, An overview of todays high-level synthesis tools. Des. Autom. Emb. Syst., pp. 1–21 (2012)

- BDTI, An Independent Evaluation of the AutoESL AutoPilot High-Level Synthesis Tool (2010). http://www.bdti.com/Resources/BenchmarkResults/HLSTCP/AutoPilot. Accessed 10 Oct 2012

- F. Winterstein, S. Bayliss, G. Constantinides, High-level synthesis of dynamic data structures: a case study using Vivado HLS, in *Proceedings of the International Conference on Field-Programmable Technology (ICFPT)* (2013), pp. 362–365

- 32. R. Nane, V.-M. Sima, C. Pilato, J. Choi, B. Fort, A. Canis, Y.T. Chen, H. Hsiao, S. Brown, F. Ferrandi, J. Anderson, K. Bertels, A survey and evaluation of FPGA high-level synthesis tools, *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*. http:// janders.eecg.toronto.edu/pdfs/tcad\_hls.pdf. Accessed 28 Feb 2016

- S. Sarkar, S. Dabral, P. Tiwari, R. Mitra, Lessons and experiences with high-level synthesis. IEEE Des. Test Comput. 26(4), 34–45 (2009)

- P. O'Hearn, J. Reynolds, H. Yang, Local reasoning about programs that alter data structures, in *Computer Science Logic*, ed. by L. Fribourg, Lecture Notes Series, in Computer Science, vol. 2142, (Springer, Heidelberg, 2001), pp. 1–19

- F.J. Winterstein, S.R. Bayliss, G.A. Constantinides, Separation logic for high-level synthesis. ACM Trans. Reconfigurable Technol. Syst. 9(2), 10:1–10:23 (2015)

- 36. F. Winterstein, K. Fleming, H.-J. Yang, J. Wickerson, G. Constantinides, Custom-sized caches in application-specific memory hierarchies, in *Proceedings of the International Conference on Field Programmable Technology (ICFPT)* (2015), pp. 144–151

- F. Winterstein, K. Fleming, H.-J. Yang, S. Bayliss, G. Constantinides, MATCHUP: memory abstractions for heap manipulating programs, in *Proceedings of the ACM/SIGDA International Symposium on Field-Programmable Gate Arrays (FPGA)* (2015), pp. 136–145

- F. Winterstein, S. Bayliss, G.A. Constantinides, Separation logic-assisted code transformations for efficient high-level synthesis, in *Proceedings of the IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM)* (2014), pp. 1–8

- F. Winterstein, S. Bayliss, G. Constantinides, FPGA-based K-means clustering using tree-based data structures, in *Proceedings International Conference on Field Programmable Logic and Applications (FPL)* (2013), pp. 1–6

- Vivado-KMeans: Hand-Written HDL Code and C-Based HLS Designs for K-means Clustering Implementations on FPGAs. https://github.com/FelixWinterstein/Vivado-KMeans. Accessed 19 Dec 2015

- K. Fleming, H.-J. Yang, M. Adler, J. Emer, The LEAP FPGA operating system," in *Proceedings* of the International Symposium on Field Programmable Logic and Applications (FPL) (2014), pp. 1–8

- 42. H.-J. Yang, K. Fleming, M. Adler, F. Winterstein, J. Emer, LMC: automatic resource-aware program-optimized memory partitioning, in *Proceedings of the ACM/SIGDA International Symposium on Field-Programmable Gate Arrays (FPGA)* (2016), pp. 128–137

- H.-J. Yang, K. Fleming, M. Adler, F. Winterstein, J. Emer, Scavenger: automating the construction of application-optimized memory hierarchies, in *Proceedings of the International Conference on Field Programmable Logic and Applications (FPL)* (2015), pp. 1–8

- The LEAP Run-time System Rapid System Integration of Your HLS Kernels. http://www. fpl2015.org/?page=tutorials. Accessed 03 Mar 2016

- 45. LEAP-HLS: Rapid System Integration of High-level Synthesis Kernels Using the LEAP FPGA Framework. https://github.com/FelixWinterstein/LEAP-HLS. Accessed 31 Aug 2015

- N. Ramanathan, J. Wickerson, F. Winterstein, G.A. Constantinides, A case for work-stealing on FPGAs with OpenCL atomics," in *Proceedings of the ACM/SIGDA International Symposium* on Field-Programmable Gate Arrays (FPGA) (2016), pp. 48–53

- 47. S.T. Fleming, D.B. Thomas, F. Winterstein, *FPGAs and Parallel Architectures for Aerospace Applications: Soft Errors and Fault-Tolerant Design*, pp. 75–90 (Springer International Publishing, Heidelberg, 2016). (ch. A Power-Aware Adaptive FDIR Framework Using Heterogeneous System-on-Chip Modules)

- E.A. Pelaez, S. Bayliss, A. Smith, F. Winterstein, D.R. Ghica, D. Thomas, G.A. Constantinides, Compiling higher order functional programs to composable digital hardware, in *Proceedings* of the IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM) (2014), pp. 234–234

## Chapter 2 High-Level Synthesis of Dynamic Data Structures

HLS promises significant shortening of the design cycle compared to a design entry at RTL. However, many HLS implementations require extensive code alterations to ensure synthesisability and to achieve latency, throughput and resource utilisation comparable to handwritten RTL designs. These are especially important for programs with 'irregular control flow' and 'complicated data dependencies'. In this chapter, we describe these terms in detail and elaborate on their implications for efficient HLS. To this end, we present a case study comparing the implementations of two algorithms for a compute-intensive machine learning application (K-means clustering). Algorithmically, both implementations solve the same problem, but they differ significantly in their computational properties: the first is a data flow-centric, 'regular' implementation with simple control flow, whereas the second is based on a recursive traversal of a pointer-linked tree data structure and uses dynamic memory allocation. The latter application thus exhibits highly 'irregular control flow' and 'complicated data dependencies'. Despite this irregularity, software implementations of this algorithm have been shown to be significantly faster than their data flow-centric counterparts because it effectively reduces the algorithmic complexity of the problem [1].

Our evaluation fits in the line of works that present designer's experiences with HLS tools. For example, a broad selection of 12 state-of-the-art HLS tools, academic and commercial, is evaluated by Meeus et al. [2]. Their overview, attesting Vivado HLS excellent test results, targets FPGA as well as ASIC flows and is based on a large set of criteria grouped into language support, ease of use, QoR and the capability of a rapid design space exploration. The goal is to perform a broad comparison across different tools mainly using a *Sobel* edge detector [3] as a test case. Sarkar et al. [4] present a more refined designer's experience with three HLS tools for ASICs using stream-based video processing applications. Their conclusion highlights the importance of fine-grained re-architecturing their test cases to optimise area and power consumption, and an evaluation by experienced users to obtain solid comparisons. BDTI present an explicit evaluation of AutoPilot (later renamed into Vivado HLS after the acquisition by Xilinx) [5]. Their evaluation uses video processing and stream-based wireless communications benchmarks, reporting QoR comparable with

<sup>©</sup> Springer International Publishing AG 2017

F. Winterstein, *Separation Logic for High-level Synthesis*, Springer Thesis, DOI 10.1007/978-3-319-53222-6\_2

manual RTL implementations. The evaluations above share the commonality that the chosen benchmark cases are data flow-centric stream-based applications with simple control flow. A recent survey in [6] compares three academic tools and one commercial HLS tool using and four data-flow centric benchmarks in addition to the CHStone [7] benchmark suite, which covers a broader spectrum of applications. Heap-manipulating code, however, is not included. In contrast to the above evaluations, with our pointer-based benchmark, we aim to operate the HLS flow on test cases outside its 'comfort zone'.

The outcome of our case study is three-fold: Firstly, we can show that the performance result obtained for software implementations can be repeated with handoptimised RTL implementations of both algorithms. This result is interesting in that irregular algorithms are often believed to be inefficient once mapped into hardware. Furthermore, it shows that the use of dynamic, pointer-linked data structures, which are central to the second algorithm, can result in very efficient FPGA applications if implemented well. Secondly, we repeat the case study with an HLS implementation using a state-of-the-art HLS tool and show that our previous result is reversed if the source code is not substantially altered prior to HLS. Thirdly, we analyse the efficiency with which the HLS tool maps specific program features into RTL and propose source-to-source transformations that improve the QoR of the irregular algorithm by a factor of eight in terms of latency, significantly narrowing the gap between HLS and hand-written RTL implementations. This chapter describes:

- An efficient RTL implementation of the irregular tree-based *K*-means clustering algorithm which preserves the algorithmic advantage over the conventional regular implementation. We show how the implementation can efficiently exploit the distributed memory architecture in FPGAs.

- A comparative case study using a data-flow centric clustering implementation and an implementation based on recursive traversal of a pointer-linked tree structure which incorporates data-dependent control flow. The case study comprises handwritten RTL and HLS implementations. Code transformations necessary to enable HLS of unsupported program features are highlighted.

- The use of on-chip dynamic memory allocation which allows us to allocate the average amount of memory required during runtime instead of statically preallocating the worst-case amount resulting in a  $57 \times$  reduction of on-chip memory resources.

- An end-to-end QoR comparison between the automatically generated RTL code for both variants and both functionally equivalent, hand-written RTL implementations.

- An analysis of how efficiently specific program features are synthesised into RTL. We propose source-to-source transformations that improve QoR by a factor of eight in terms of latency.

The two algorithms for *K*-means clustering form the basis of our case study. Figure 2.1 shows our design flow. The initial C++ model is modified in order to include custom precision for operands of the basic arithmetic operations. From this model, we implement a hand-written RTL design written in VHDL (bottom branch, Sect. 2.3) and a C++-based HLS design (top branch). The HLS

Fig. 2.1 Design flow of the case study

implementation requires further code refactoring which we discuss in Sect. 2.4. The generated and hand-crafted RTL design entries are verified using standard RTL simulation tools. Finally, QoR is compared in terms of latency and resource usage taken from the placed and routed FPGA designs (Sect. 2.5). The evaluation flow in Fig. 2.1 is repeated for both clustering algorithms. The following section discusses both algorithms.

#### 2.1 Background

The test cases we chose for this case study are two implementations of a clustering application, a technique for unsupervised partitioning of a data set commonly used in a wide range of applications, such as machine learning and data mining [8, 9], radar tracking [10], image colour or spectrum quantisation [11–14]. A popular technique for finding clusters in a data set is *K*-means clustering, which partitions the *D*-dimensional point set  $X = \{x_j\}, j = 1, ..., N$  into clusters  $\{S_i\}, i = 1, ..., K$ , where *K* is provided as a parameter. The goal is to find the optimal partitioning which minimises the total sum of squared Euclidean distances (squared-error distortion) given in (2.1) where  $\mu_i$  is the geometric centre (centroid) of  $S_i$ .

$$J(\{S_i\}) = \sum_{i=1}^{K} \sum_{x_j \in S_i} \|x_j - \mu_i\|^2$$

(2.1)

Finding optimum solutions to this problem is NP-hard [15]. A popular heuristic version uses an iterative refinement scheme. The standard algorithm begins by choosing *K* initial centres  $Z = {\mu_1, ..., \mu_K}$  sampled randomly from the point set. The set *Z* is iteratively refined until it no longer changes. On each iteration, it splits *X* into *K* partitions, according to which is the nearest mean of each partition. These means (geometrical centres) form the next generation of *Z* (*Z'*). Using one algorithm for this problem, which we refer to as *Lloyd's algorithm*,  $N \cdot K \cdot L$  distances in *D*dimensional space are computed where *N* is the number of data points and *L*, the number of required iterations. Listing 1 shows pseudo code of the main processing loop for one iteration of Lloyd's algorithm. Line 12 searches among *K* candidate

#### Listing 1 Main kernel of Lloyd's algorithm (one clustering iteration).

1: Parameters: 2: N, K3: Input: 4: point set  $X = \{x_1, x_2, \dots, x_N\}$ 5: initial centre set  $Z = \{\mu_1, \mu_2, \dots, \mu_K\}$ 6: Output: 7: new centre set  $Z' = \{\mu'_1, \mu'_2, ..., \mu'_K\}$ 8: Variables: 9: centroid information  $C = \{c_1, c_2, \dots, c_K\}$ 10: function LLOYDS for all  $x_i \in \{x_1, x_2, ..., x_N\}$  do 11: ▷ iterate over all data points  $i \leftarrow \operatorname{argmin}_{i',\mu_{i'}\in Z}(||x_j - \mu_{i'}||^2)$ 12:  $\triangleright$  find closest centre to  $x_i$  among K candidates 13:  $c_i \leftarrow$  select *i* th element in C 14:  $c_i.wgtCent \leftarrow c_i.wgtCent + x_i$ 15:  $c_i.count \leftarrow c_i.count + 1$ 16: update  $c_i$  in C 17: end for 18: for all  $c_i \in C$  do ▷ update centre positions 19:  $\mu'_i \leftarrow c_i.wgtCent/c_i.count;$ 20: end for 21: end function

centres for the closest centre to a data point  $x_i$ . The index *i* of this centre is used to update the correct entry in the centroid information table *C* (Lines 13–16). *C* contains *K* vector sums of data points which we refer to as 'weighted centroids' (*wgtCent*). After all data points have been processed, the final output centre set  $\{\mu'_1, \mu'_2, \ldots, \mu'_K\}$  is computed from the weighted centroids in *C* (Lines 18–20).

In contrast to massively parallel hardware implementations, sophisticated software implementations have been proposed which gain speed-up from search space reductions. Kanungo et al. [1] present one possible implementation. Their *filtering algorithm* organises the data points in a multi-dimensional binary search tree, called a 'kd-tree', and finds nearest centres at each iteration using a tree traversal. To this end, the point set is recursively divided into two subsets. In each step, the axis-aligned bounding box of the subset is computed and subdivided. This leads to a (generally not perfectly balanced) binary kd-tree structure whose root node represents the bounding box of all data points and whose children nodes represent recursively refined, nonempty disjoint bounding boxes. Each tree node stores the bounding box (*bndBox*) information as well as the number (*count*) and the vector sum of its associated points (the weighted centroid, *wgtCent*) which is used to update the cluster centres when each iteration completes. The weighted centroid of leaf nodes is the data point itself.

Listing 2 shows a simplified version of the recursive kernel function of the filtering algorithm for one iteration. During clustering, the tree is traversed starting from the root node. The set of input centres in Lloyd's algorithm is replaced by sets of

candidates for the closest centre to a subset of data points. The algorithm propagates multiple candidate sets down the tree. These are of variable size and are created and disposed at run-time. At each non-terminal visited tree node, the closest candidate centre to the mid point (*midPoint*) of the bounding box is found. Some of the remaining candidates are pruned if no part of the bounding box is closer to them than the closest centre (Line 22). The pruning greatly reduces the number of computed distances since the average number of 'close' cluster-centre candidates is significantly smaller than *K*. Additionally, entire sub-trees can be pruned if only one candidate remains. As the point set does not change during clustering, the kd-tree needs to be built up only once and the additional overhead is amortised over all iterations. In fact, our profiling results show that, on average, the tree construction demands less than 2% of the total computation required. Therefore, we perform the pre-processing in software and the FPGA accelerator discussed in the following focuses only on the tree traversal phase.

In light of this case study, we identify the most important features of both applications. Because the min-search in Listing 1 (Line 12) is implemented as a for-loop over K centres, the main kernel of Lloyd's algorithm consists of two nested forloops with constant bounds. The simple control flow and inherent parallelism at the granularity of distance computations makes the computationally expensive algorithm suitable for hardware implementations so as to accelerate K-means clustering for real-time implementations if N and K are large. Computational parts of the filtering algorithm in Listing 2 are the closest centre searches (Lines 14, 20) and the candidate pruning (Line 22, containing two distance calculations), and the centroid buffer update. The loops in the min-searches and candidate pruning have variable bounds  $2 \le k \le K$ . The implementation uses dynamic memory allocation (Line 21) and de-allocation (Lines 32, 36) enclosed in data-dependent conditionals. Memory space is freed upon backward traversal, i.e. after an allocated centre set has been read twice. The implementation uses recursive function calls (beyond tail recursion) which requires the presence of a *stack*. The stack is implicitly handled in the software program, but it needs to be explicitly implemented in an FPGA application. The data passed between recursive instances are the tree node u and the set of candidate centre set Z.

Previous hardware implementations of Lloyd's algorithm are proposed in [14, 16–19]. Pioneering work by Leeser et al. [16] implemented FPGA-clustering for the analysis of hyperspectral images. Their approach trades clustering quality for hardware resource consumption by replacing the Euclidean distance norm with multiplierless Manhattan and Max metrics. This trade-off is extended to bit width truncations on the input data by Estlick et al. [14] who report a speed-up of up to  $200 \times$  over the software implementation. More recent work in [17] builds on the same framework and extends it by incorporating a hybrid fixed- and floating-point arithmetic architecture. These approaches aim to gain acceleration from an increased amount of parallel hardware resources for distance computations and nearest centre search.

**Listing 2** Main kernel of the filtering algorithm (one clustering iteration) [1].

1: Parameters: 2: N, K3: Input: 4: kd-tree 5: initial centre set  $\{\mu_1, \mu_2, \ldots, \mu_K\}$ 6: Output: 7: new centre set  $Z' = \{\mu'_1, \mu'_2, \dots, \mu'_K\}$ 8: Variables: 9: node in the kd-tree *u* 10: multiple sets of candidates for the closest centre to a point cloud (Z)11: centroid information  $C = \{c_1, c_2, \dots, c_K\}$ 12: **function** FILTER(u, Z)13: if *u* is leaf then 14:  $i^* \leftarrow \operatorname{argmin}_{i',\mu_{i'} \in \mathbb{Z}}(||u.wgtCent - \mu_{i'}||^2)$  $\triangleright$  find closest centre to *u.wgtCent* 15:  $c_{i^*} \leftarrow$  select  $i^*$ -th element in C 16:  $c_{i^*}.wgtCent \leftarrow c_{i^*}.wgtCent + u.wgtCent$ 17:  $c_{i^*}.count \leftarrow c_{i^*}.count + 1$ 18: update  $c_{i*}$  in C 19: else 20:  $i^* \leftarrow \operatorname{argmin}_{i',\mu_{i'} \in \mathbb{Z}}(||u.midPoint - \mu_{i'}||^2)$ ▷ find closest centre to *u.midPoint* 21:  $Z_{new} \leftarrow \mathbf{new}$  centre set  $\triangleright$  allocate new centre set (empty) 22: prune candidate centres for all  $\mu_i \in Z$  do 23: if pruningTest( $i^*$ ,  $\mu_i$ , *u.bndBox*) is false then 24:  $Z_{new} \leftarrow Z_{new} \cup \{\mu_i\};$  $\triangleright$  insert surviving candidates into  $Z_{new}$ 25: end if 26: end for 27: if  $|Z_{new}| = 1$  then 28:  $c_{i^*} \leftarrow$  select  $i^*$ -th element in C 29:  $c_{i^*}.wgtCent \leftarrow c_{i^*}.wgtCent + u.wgtCent$ 30:  $c_{i^*}.count \leftarrow c_{i^*}.count + u.count$ 31: update  $c_{i^*}$  in C delete  $Z_{new}$ 32:  $\triangleright$  immediately delete allocated  $Z_{new}$ 33: else ⊳ recurse on children 34: FILTER(u.left,  $Z_{new}$ ); 35: FILTER( $u.right, Z_{new}$ ); 36: delete  $Z_{new}$  $\triangleright$  delete allocated  $Z_{new}$  on the way back 37: end if 38: end if 39: end function 40: for all  $c_i \in C$  do ▷ update centre positions 41:  $\mu'_i \leftarrow c_i.wgtCent/c_i.count;$ 42: end for

Contrary to these works, the first contribution in this thesis chapter is an efficient implementation of the filtering algorithm, which gains acceleration largely from search space pruning. Chen et al. [20] present a VLSI implementations for K-means clustering which is notable in that it, in line with our approach, recursively splits the data point set into two subspaces using conventional 2-means clustering. Logically,

this creates a binary tree which is traversed in a breadth-first fashion and results in computational complexity proportional to  $\log_2 K$ . This approach, however, does not allow any pruning of candidate centres. Saegusa et al. [12] present a simplified kd-tree-based implementation for *K*-means image clustering. The data structure stores the best candidate centre (or generally a few 'best' candidates) at its leaf nodes and is looked up for each data point. The tree is built independently of the data points, i.e. the pixel space is subdivided into regular partitions which leads to 'empty' pixels being recursively processed. Other disadvantages are that the tree needs to be rebuilt at the beginning of each iteration and that the centre lists are not pruned during tree traversal in the build phase, which are essential features of the filtering algorithm.

#### 2.2 Analysis of the Filtering Algorithm

We analyse several properties of the filtering algorithm that provide insight into the advantage over Lloyd's algorithm. To this end, we profile a software implementation of the algorithm. The input data sets that we use throughout this chapter are point sets of N = 16,384 three-dimensional real-valued samples. The data points are distributed among 128 centres following a normal distribution with varying standard deviation  $\sigma$ , whereas the centre coordinates are uniformly distributed over the interval [-1, 1]. Finally, the data points are converted to 16bit fixed-point numbers. We choose K = 128 initial centres sampled randomly from the data set and run the algorithm either until convergence of the objective function or until a maximum of 30 iterations are reached. In addition to synthetic input data, we include a working set with N = 16,384 randomly sampled pixels from the well-known Lena benchmark image and quantise the colour space into K = 128 clusters. Note that the clustering output is exactly the same for both the implementation of Lloyd's and the filtering algorithm.

The filtering algorithm can be divided into two phases: building the tree from the point set (pre-processing), and the repeated tree traversal and centre update (clustering phase). In order to obtain information about the computational complexity of both parts, we profile the software implementation of the algorithm using synthetic input data. Here, we chose the number of Euclidean distance computations performed as our metric for computational complexity. Since the tree creation phase does not compute any distances but performs mainly dot product computations and comparisons, we introduce distance computation equivalents (DCEs) to obtain a unified metric for both parts which combines several operations which are computationally equivalent. Table 2.1 shows the profiling results of the computational complexity of the filtering algorithm broken down into clustering and pre-processing phases for different working sets. The parameter  $\sigma$  is varied such that the synthetic input data ranges from well-distinguished clusters ( $\sigma = 0.05$ ) to a nearly unclustered point set ( $\sigma = 0.35$ ). For all cases, the number of DCEs (2% geometric mean). Because of the small contribution of

| Input data<br>N = 16, 384,<br>K = 128 | DCEs in clustering | DCEs in pre-processing | Contribution of<br>pre-processing (%) |

|---------------------------------------|--------------------|------------------------|---------------------------------------|

| Synthetic $\sigma = 0.05$             | 1,09,207           | 4963                   | 4.3                                   |

| Synthetic $\sigma = 0.10$             | 1,56,464           | 4712                   | 2.9                                   |

| Synthetic $\sigma = 0.15$             | 2,12,670           | 4574                   | 2.1                                   |

| Synthetic $\sigma = 0.20$             | 2,59,146           | 4494                   | 1.7                                   |

| Synthetic $\sigma = 0.25$             | 2,94,173           | 4423                   | 1.5                                   |

| Synthetic $\sigma = 0.30$             | 3,21,841           | 4432                   | 1.4                                   |

| Synthetic $\sigma = 0.35$             | 3,39,831           | 4424                   | 1.3                                   |

| Lena benchmark<br>(subset)            | 2,24,418           | 4923                   | 2.1                                   |

Table 2.1 Computational complexity of the filtering algorithm broken down into clustering and pre-processing phases

the pre-processing, we perform this part in software and the FPGA implementation described in the following section focuses on the tree traversal phase only.

We also evaluate the search space pruning. The major complexity reduction is due to the fact that the repeated searches for the closest centre need to consider significantly fewer centres than Lloyd's algorithm for which this number is always K. Figure 2.2 (left) shows the frequency of candidate centre set sizes averaged over all synthetic cases above. During tree processing, most sets contain only 2 or 3 centres and the average centre set size is 4.36 (3.78 for the Lena image benchmark), which shows the effectiveness of the search space pruning. We quantify the overall search complexity of the filtering algorithm in terms of the aggregate number of *node-centre pairs*, i.e. the cumulative number of candidate centres processed at the visited tree nodes per clustering iteration. This number is sensitive to the input data.

**Fig. 2.2** Left Frequency of candidate centre set sizes for synthetic input data. Right Computational complexity of the filtering algorithm in terms of node-centre pairs (Lloyd's algorithm has a constant complexity of  $209.7 \times 10^4$  point-centre pairs for this data set)

Figure 2.2 (right) shows the number of node-centre pairs over different values of  $\sigma$  in the synthetic data sets. The complexity ranges from 31,399 to 94,590. We also include the Lena benchmark with 61,230 node-centre pairs for a comparison with real-world data. For Loyd's algorithm, an equivalent metric of data point-centre pairs can be defined which is  $N \cdot K = 20,97,152$  for all input sets in Fig. 2.2. Even for unfavourable input data ( $\sigma = 0.35$ ), the filtering algorithm thus achieves a 22× reduction of search complexity. In a sequential software implementation [1], this reduction translates directly into a run-time advantage of the filtering algorithm. The next sections investigate if, how, and to what extent this result can be reproduced in hardware implementations.

#### 2.3 **RTL Implementations**

This section describes efficient hand-crafted FPGA implementations of Lloyd's and Kanungo's filtering algorithm implementations, which will be compared in Sect. 2.5.1. Both RTL implementations are fully pipelined designs and their computational parts mainly consist of the same basic elements, Euclidean distance and dot product computations, but their control structures and memory architectures are substantially different. We made the source code of the RTL implementations discussed below available in an open source repository.<sup>1</sup> The following description motivates later discussion of how we direct the HLS flow to produce competitive designs from a C description. Specific features discussed here and implemented later in the HLS flow (Sect. 2.4) will disclose particular limitations.

#### 2.3.1 Lloyd's Algorithm