# PLD Based Design with VHDL

RTL Design, Synthesis and Implementation

# PLD Based Design with VHDL

### Vaibbhay Taraate

# PLD Based Design with VHDL

RTL Design, Synthesis and Implementation

Vaibbhav Taraate Pune, Maharashtra India

ISBN 978-981-10-3294-3 ISBN 978-981-10-3296-7 (eBook) DOI 10.1007/978-981-10-3296-7

Library of Congress Control Number: 2016958476

### © Springer Nature Singapore Pte Ltd. 2017

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

This Springer imprint is published by Springer Nature

The registered company is Springer Nature Singapore Pte Ltd.

The registered company address is: 152 Beach Road, #22-06/08 Gateway East, Singapore 189721, Singapore

### **Preface**

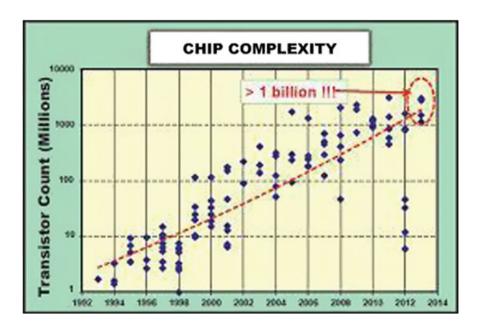

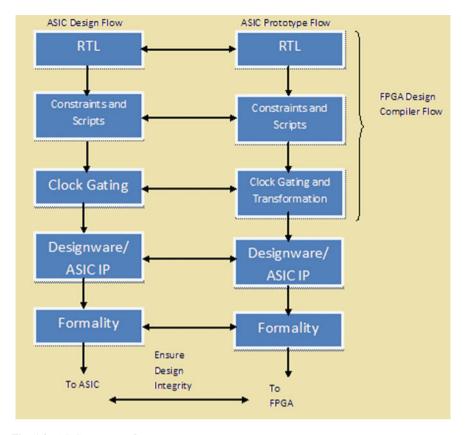

In the present decade, the complexity of the ASIC and FPGA design has grown rapidly. Due to that there is need of the intelligent and complex devices, and hence the FPGA prototyping area has evolved during this decade.

Major FPGA vendors such as XILINX and Altera (Intel FPGA) have come up with the complex FPGAs which are required for design and realization of the system on chip (SOC). During this decade, the era of miniaturization has lot many challenges. The major challenges are to design and deliver the intelligent products for lesser cost, high speed, less area, and less power.

Under such circumstances for the idea or product feasibility, the complex FPGAs are used and the complexity of FPGA architecture has grown in the past decade. Even the multiple FPGA designs are used to validate the complex SOCs. For easy understanding of the FPGA designs and ASIC prototyping using FPGAs, this book is organized. This book covers the design for the lower gate count to higher gate count designs. Even this book is written in such a way that it can give information about the VHDL, synthesis, FPGAs, and ASIC prototyping.

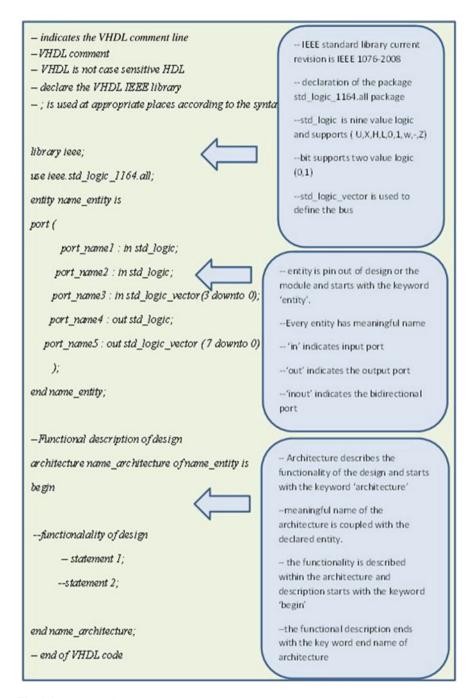

Chapter 1 of this book discusses the evolution of the logic design, need of HDL, and differences between the VHDL and other higher level languages, and even this chapter describes about the different modeling styles using VHDL.

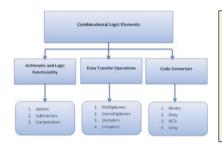

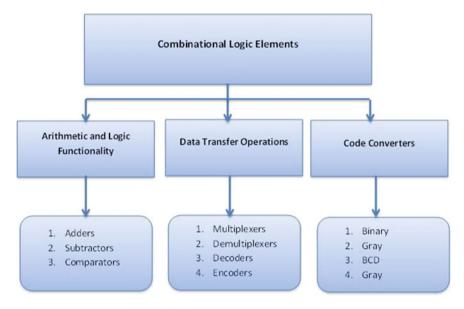

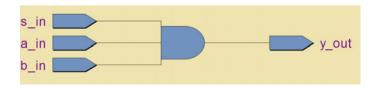

Chapter 2 of this book describes about the basic combinational elements and their use in the design. Even this chapter describes how to write synthesizable RTL using the VHDL constructs. This chapter is useful for the beginners to understand about the basic VHDL constructs and the synthesis outcome of few low gate count designs.

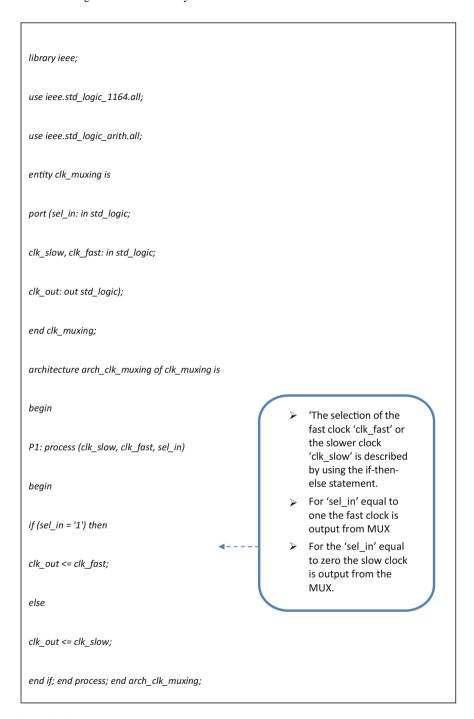

Chapter 3 discusses the key VHDL constructs such as processes, signals, and variables, when else, with select, if-then-else and case. Even this chapter covers the practical scenarios and use of these constructs.

Chapter 4 describes the how to write an efficient RTL using VHDL. Even this chapter covers the design for the combinational logic such as multibit adders, multiplexers, decoders, and encoders. The synthesis for the RTL design using VHDL is covered with the detailed explanation and practical scenarios.

viii Preface

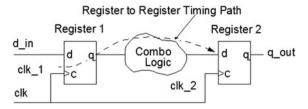

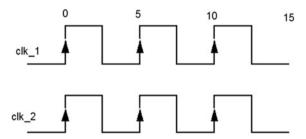

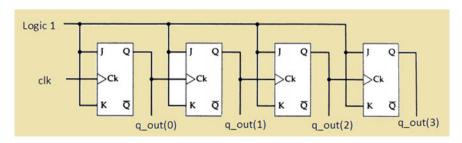

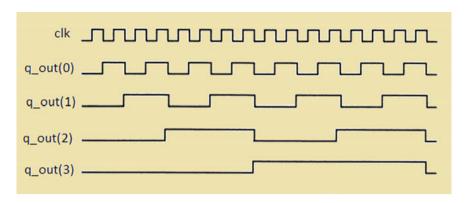

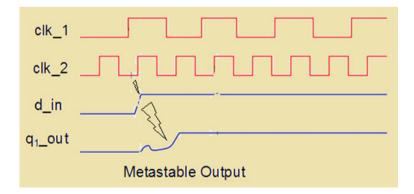

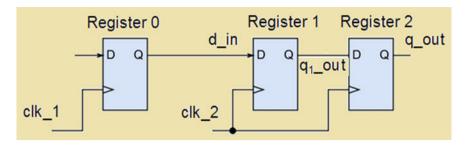

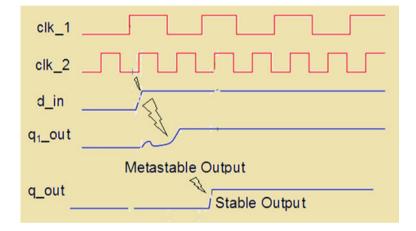

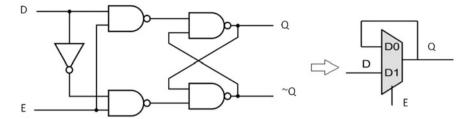

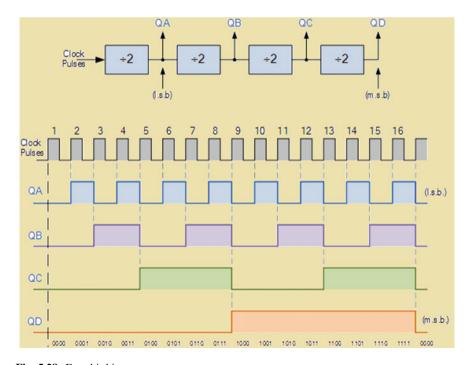

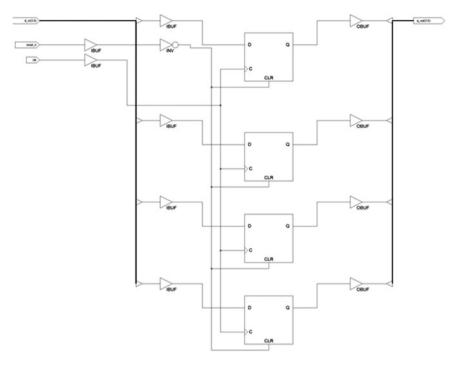

Chapter 5 covers the sequential design scenarios and the RTL using VHDL for the latches and flip-flops. Even this chapter covers the BCD counters, binary counters, gray counters, ring counters, Johnson counters and the RTL design and synthesis for the same. This chapter has information about the timing parameters and timing analysis for the synchronous sequential designs. This chapter even gives information about the basics of asynchronous and multiple clock domain designs and the issues like metastability and how to overcome those during design cycle.

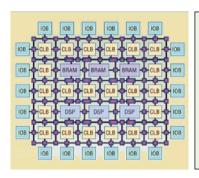

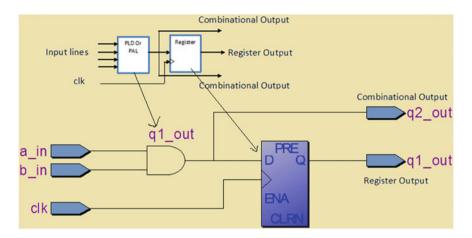

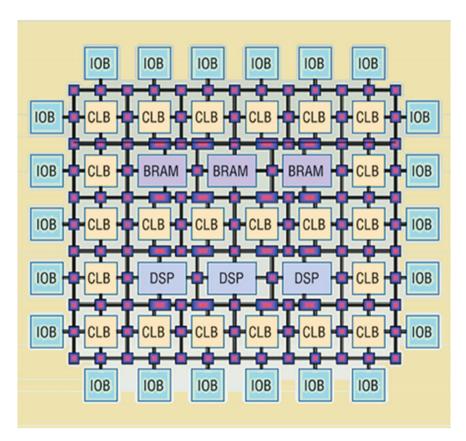

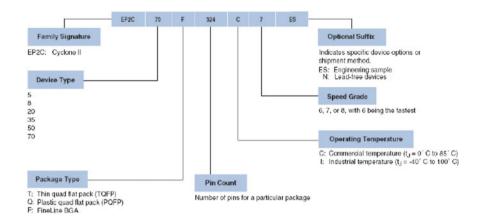

Chapter 6 covers the PLD-based designs and the detail practical-oriented examples and scenarios for the design using SPLDs, CPLDs, and FPGAs. This chapter covers the XILINX and ALTERA (Intel) FPGA architectures and their use in the design and prototyping. The vendor-specific design guidelines are covered in this chapter.

Chapter 7 covers the VHDL constructs and the use of VHDL for the verification and simulation of the design. This chapter is useful to understand the test benches and how to simulate the design for early detection of bugs. Even this chapter covers the practical issues in the design verification using practical scenarios and examples.

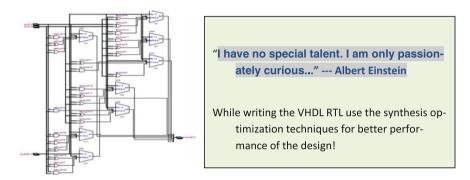

Chapter 8 covers the design and coding guidelines for the PLD-based designs. How to use the VHDL for the efficient design is explained in detail with the practical scenarios and synthesizable VHDL constructs. This chapter covers techniques such as grouping, parallel and concurrent logic, logic duplications, and resource sharing. Even this chapter covers the low-power basics as clock gating and clock enabling.

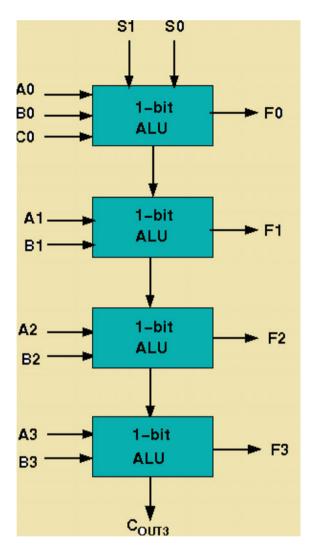

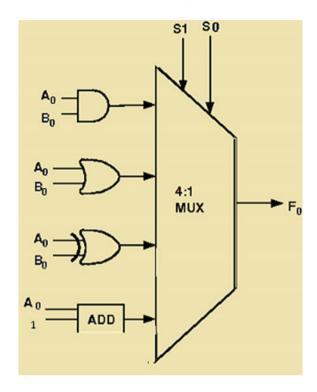

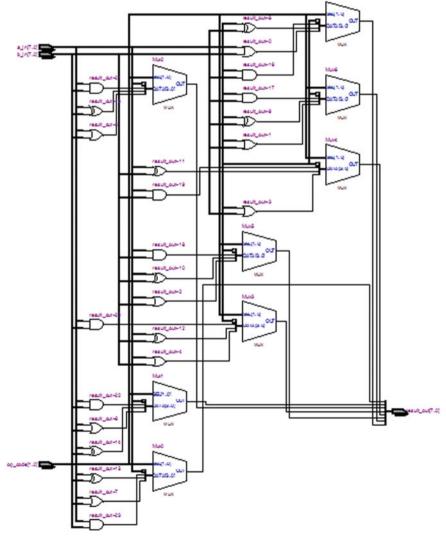

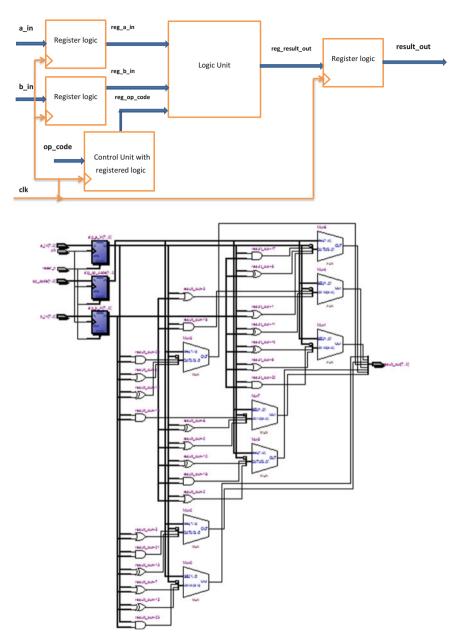

Chapter 9 covers the complex designs such as multipliers, barrel shifters, arbiters and the processor logic as ALU, and the other basic protocols. This chapter is useful to understand the synthesis issues in the complex designs and how to overcome those using the techniques described in Chap. 7.

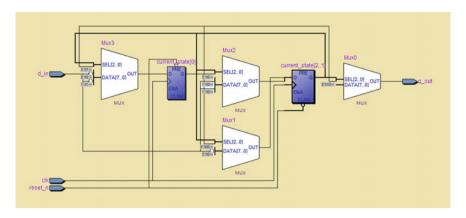

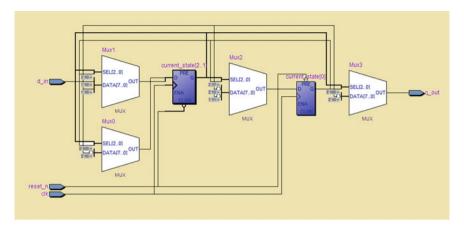

Chapter 10 discusses the finite state machines (FSMs) using the VHDL. The Moore and Mealy machines and their use to code the sequence detectors and counters are described in this chapter. Even the FSM synthesis issues and how to improve the design performance are discussed with the practical scenarios. Even this chapter covers the FSM synthesis guidelines and FSM optimization techniques used while prototyping ASICs using the complex FPGAs.

Chapter 11 covers VIVADO based design flow and case study using VIVADO for the design implementation. The case study of FIFO is covered in this chapter.

Chapters 1–11 are organized in such a way that it covers the small gate count RTL using VHDL to the complex design using VHDL with the meaningful scenarios. This book is useful for the beginners, RTL design engineers, and professionals. I hope that this book can give you the excellent understanding of VHDL constructs and use of VHDL in ASIC prototyping!

Pune, India Vaibbhav Taraate

### Acknowledgements

This book is possible due to direct and indirect contribution of many people. While writing this book, I got the great help from many people. I am thankful to all my students to whom I have taught this subject over past almost 15 years.

I am thankful to my wife Somi for her sacrifices during the period of writing this book. Although Somi was hospitalized for three months after returning from the hospital, she has helped me in finding the grammatical mistakes and even corrected initial proofs of this book.

I am very much thankful to my dearest friend Ishita Thaker (Ish) for her indirect help and motivation while writing this book.

I am very much thankful to dearest Kaju for the great wishes and prayers.

Especially I am thankful to my Son Siddesh and my daughter Kajal for understanding me during this period and for helping me with few suggestions for the representation of diagrams.

This book would not have been possible without the help of Swati Meherishi and Aparajita Singh at Springer.

I am thankful to all the Springer staff, especially Praveen V for the review of this book and for the easy-to-understand outline of this book.

Finally, in advance, I am thankful to all the readers and buyers for buying and enjoying this book!

## **Contents**

| 1 | Intro | duction to HDL                               |

|---|-------|----------------------------------------------|

|   | 1.1   | History of HDL                               |

|   | 1.2   | System and Logic Design Abstractions         |

|   | 1.3   | ASIC Prototyping                             |

|   | 1.4   | Integrated Circuit Design and Methodologies  |

|   |       | 1.4.1 RTL Coding                             |

|   |       | 1.4.2 Functional Verification                |

|   |       | 1.4.3 Synthesis                              |

|   |       | 1.4.4 Physical Design                        |

|   | 1.5   | Programming Language Verses HDL              |

|   |       | 1.5.1 VHDL Evolution and Popularity          |

|   | 1.6   | Design Description Using VHDL                |

|   |       | 1.6.1 Structural Design                      |

|   |       | 1.6.2 Behavior Design                        |

|   |       | 1.6.3 Synthesizable RTL Design 17            |

|   | 1.7   | Key VHDL Highlights and Constructs           |

|   | 1.8   | Summary                                      |

| 2 | Basic | c Logic Circuits and VHDL Description        |

|   | 2.1   | Introduction to Combinational Logic          |

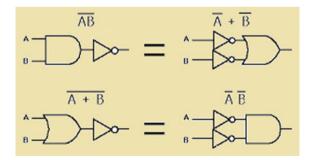

|   | 2.2   | Logic Gates and Synthesizable RTL Using VHDL |

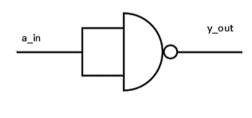

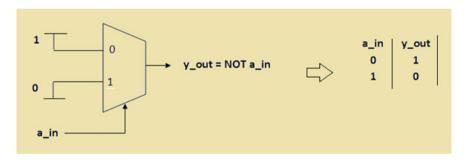

|   |       | 2.2.1 NOT or Invert Logic                    |

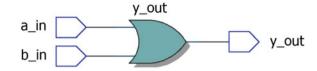

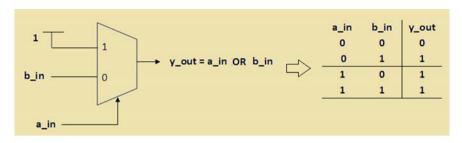

|   |       | 2.2.2 Two-Input OR Logic                     |

|   |       | 2.2.3 Two-Input NOR Logic                    |

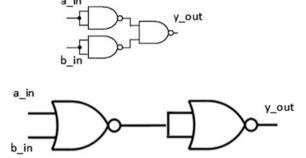

|   |       | 2.2.4 Two-Input AND Logic                    |

|   |       | 2.2.5 Two-Input NAND Logic                   |

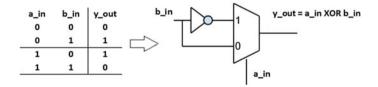

|   |       | 2.2.6 Two-Input XOR Logic                    |

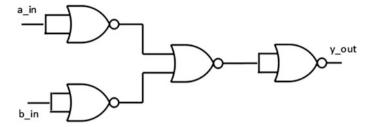

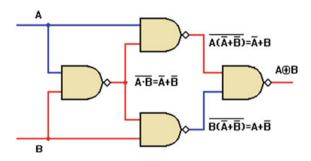

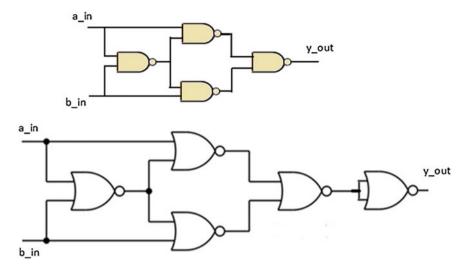

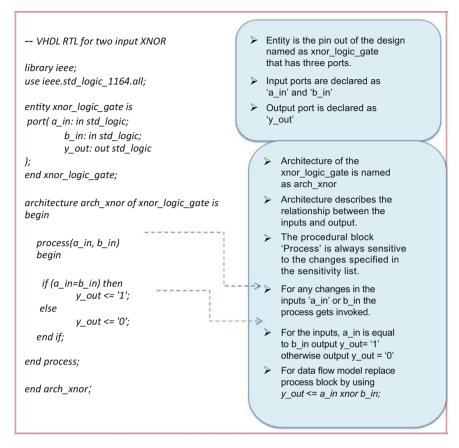

|   |       | 2.2.7 Two-Input XNOR Logic                   |

|   |       | 2.2.8 Tri-State Logic                        |

xii Contents

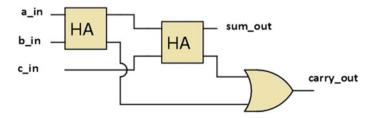

|   | 2.3  | Adder .  |                                         | 40       |

|---|------|----------|-----------------------------------------|----------|

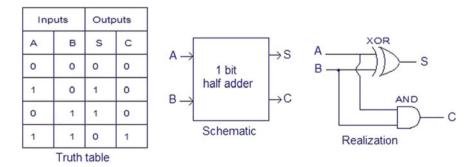

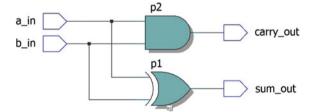

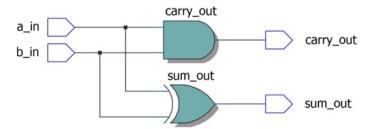

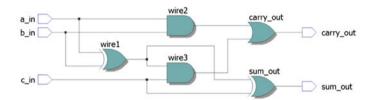

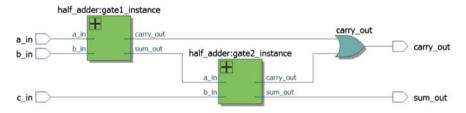

|   |      | 2.3.1    | Half Adder                              | 40       |

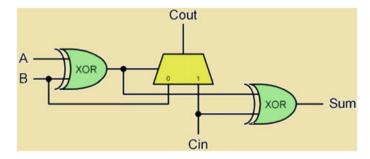

|   |      | 2.3.2    | Full Adder                              | 42       |

|   | 2.4  |          | onverters                               | 44       |

|   |      | 2.4.1    | Binary-to-Gray Code Converter           | 44       |

|   | 2.5  | 2.4.2    | Gray-to-Binary Code Converter           | 46<br>47 |

|   | 2.5  | Summa    | ry                                      | 4/       |

| 3 | VHD  |          | ey Important Constructs                 | 49       |

|   | 3.1  |          | Design Paradigm                         | 50       |

|   | 3.2  | Multiple | e Architectures and Configuration       | 53       |

|   |      | 3.2.1    | Multiple Architecture and Configuration | 54       |

|   | 3.3  | Objects  | and Data Types                          | 55       |

|   |      | 3.3.1    | Scalar Data Types                       | 55       |

|   |      | 3.3.2    | Composite Data Types                    | 57       |

|   |      | 3.3.3    | Data Objects                            | 59       |

|   |      | 3.3.4    | Constants                               | 59       |

|   | 3.4  | Signal A | Assignments                             | 60       |

|   |      | 3.4.1    | Signal Assignments Example              | 61       |

|   | 3.5  | Variable | e Assignment                            | 61       |

|   |      | 3.5.1    | Variable Assignments Example            | 63       |

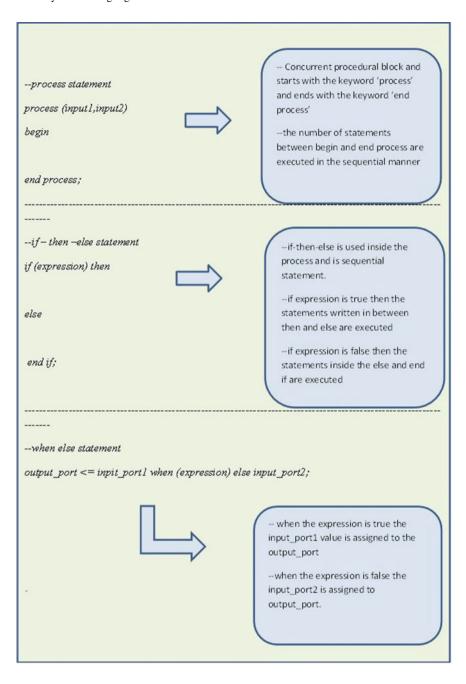

|   | 3.6  | Concurr  | rent Constructs                         | 64       |

|   |      | 3.6.1    | When Else                               | 64       |

|   |      | 3.6.2    | With Select                             | 66       |

|   |      | 3.6.3    | Process                                 | 66       |

|   | 3.7  | Sequent  | tial Constructs                         | 69       |

|   |      | 3.7.1    | If Then Else                            | 70       |

|   |      | 3.7.2    | Nested If Then Else                     | 73       |

|   |      | 3.7.3    | Case                                    | 75       |

|   | 3.8  | Modelir  | ng Sequential Logic                     | 76       |

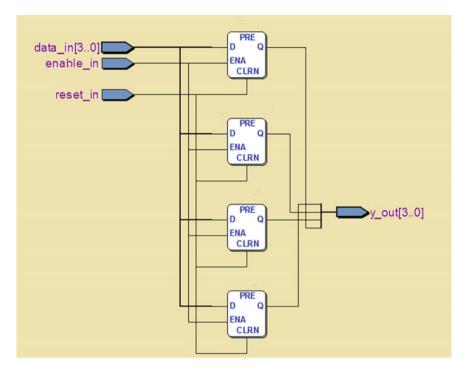

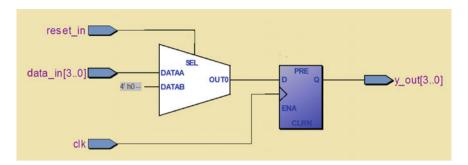

|   |      | 3.8.1    | Four-Bit Register                       | 77       |

|   |      | 3.8.2    | Four-Bit Latch                          | 78       |

|   | 3.9  | Wait St  | atements                                | 78       |

|   |      | 3.9.1    | Wait On                                 | 78       |

|   |      | 3.9.2    | Wait For                                | 80       |

|   |      | 3.9.3    | Wait Until                              | 81       |

|   | 3.10 | Loops.   |                                         | 82       |

|   |      | 3.10.1   | Loop                                    | 82       |

|   |      | 3.10.2   | While Loop                              | 83       |

|   |      | 3.10.3   | For Loop.                               | 83       |

|   | 3.11 |          | ry                                      | 85       |

|   |      |          |                                         | 85       |

|   |      |          |                                         |          |

Contents xiii

| 4 | Com        | bination | nal Logic Design Using VHDL Constructs             | 87         |

|---|------------|----------|----------------------------------------------------|------------|

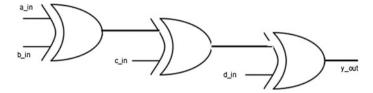

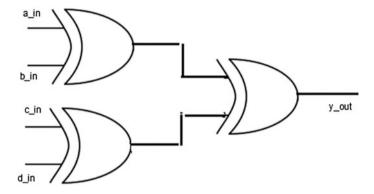

|   | 4.1        | Combi    | national Logic and Delays                          | 88         |

|   |            | 4.1.1    | Cascade Combinational Logic                        | 89         |

|   |            | 4.1.2    | Parallel Combinational Logic                       | 90         |

|   | 4.2        | Arithm   | netic Circuits                                     | 90         |

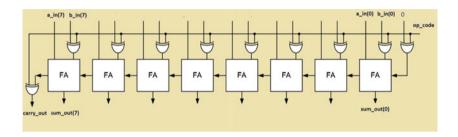

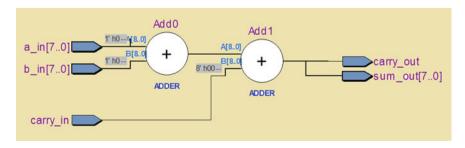

|   |            | 4.2.1    | Multibit Adder                                     | 91         |

|   |            | 4.2.2    | Multibit Adder–Subtractor                          | 92         |

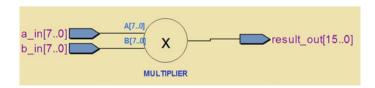

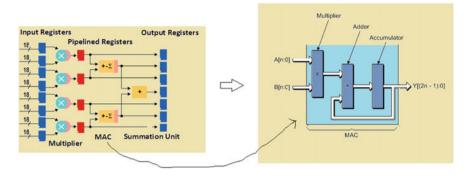

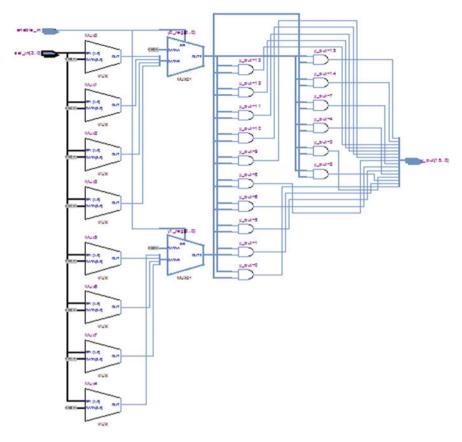

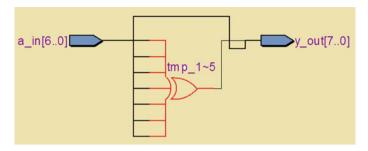

|   |            | 4.2.3    | Multiplier                                         | 94         |

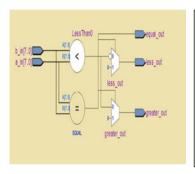

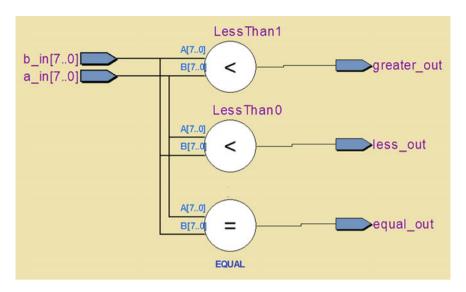

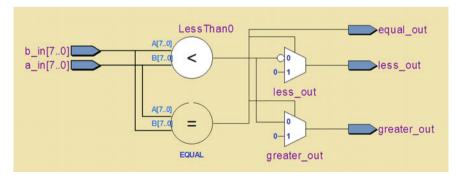

|   |            | 4.2.4    | Comparators                                        | 95         |

|   | 4.3        | Code (   | Converter                                          | 99         |

|   |            | 4.3.1    | Binary-to-Excess-3 Code Converter                  | 99         |

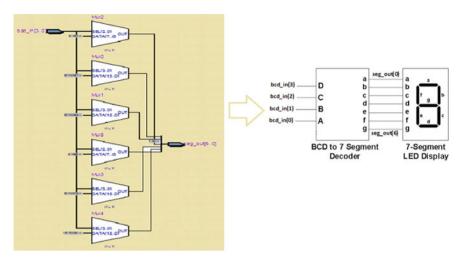

|   |            | 4.3.2    | BCD-to-Seven-Segment Decoder                       | 101        |

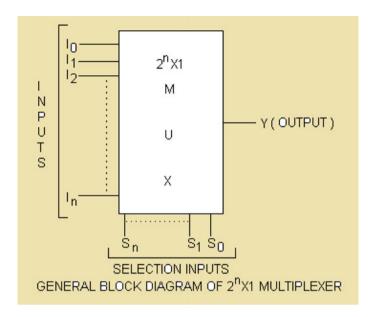

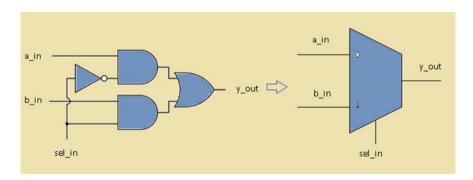

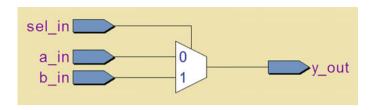

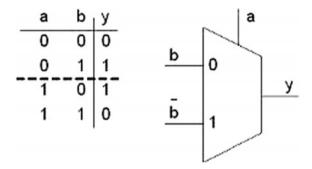

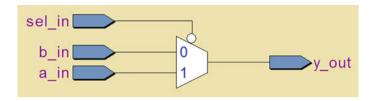

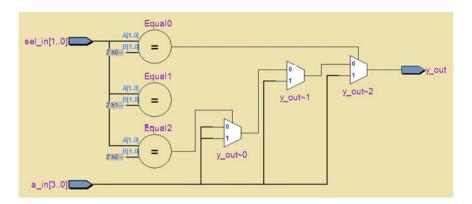

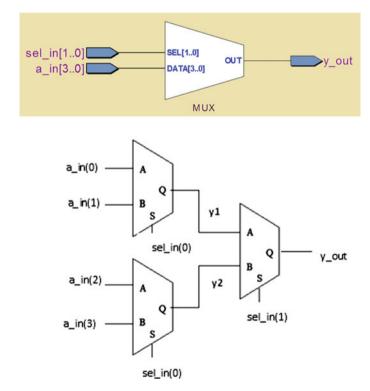

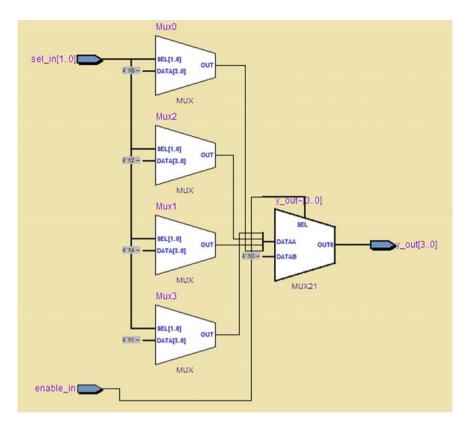

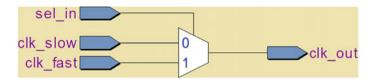

|   | 4.4        | Multip   | lexers                                             | 103        |

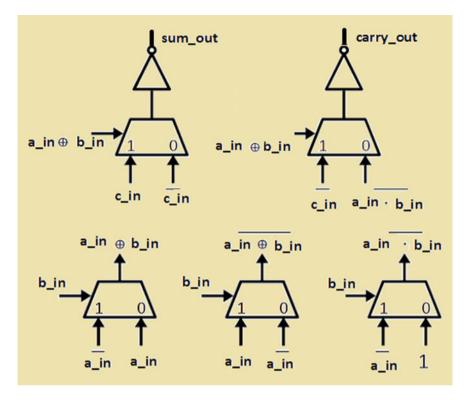

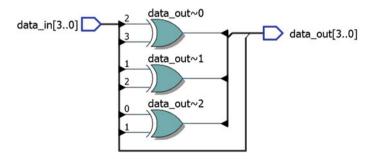

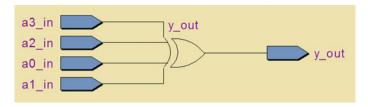

|   |            | 4.4.1    | Multiplexer as Universal Logic                     | 105        |

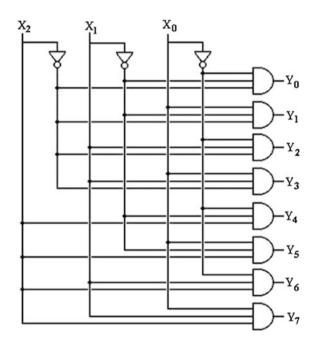

|   | 4.5        | Decode   | ers                                                | 110        |

|   |            | 4.5.1    | 3 Line to 8 Decoder with Enable Using 'Case'       | 110        |

|   |            | 4.5.2    | 2 Line to 4 Decoder with Enable Using 'Case'       | 115        |

|   | 4.6        | Encode   | ers                                                | 116        |

|   |            | 4.6.1    | Priority Encoders                                  | 116        |

|   | 4.7        | Summa    | ary                                                | 122        |

| _ | C          |          | •                                                  | 100        |

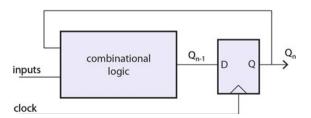

| 5 |            |          | ogic Design                                        | 123<br>124 |

|   | 5.1        |          | ntial Logic                                        | 124        |

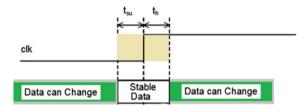

|   |            | 5.1.1    | Metastability and Timing Parameters for the        | 126        |

|   | 5.2        | D L ete  | Sequential Logic                                   | 120        |

|   | 3.2        |          | thes in the Design                                 |            |

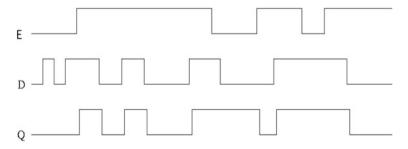

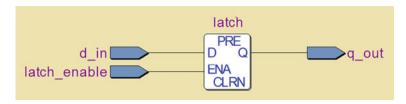

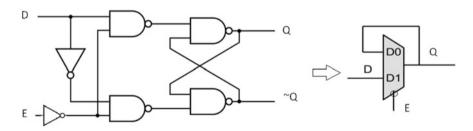

|   |            | 5.2.1    | Positive Level Sensitive D-Latch.                  | 130        |

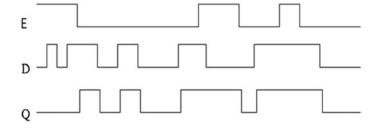

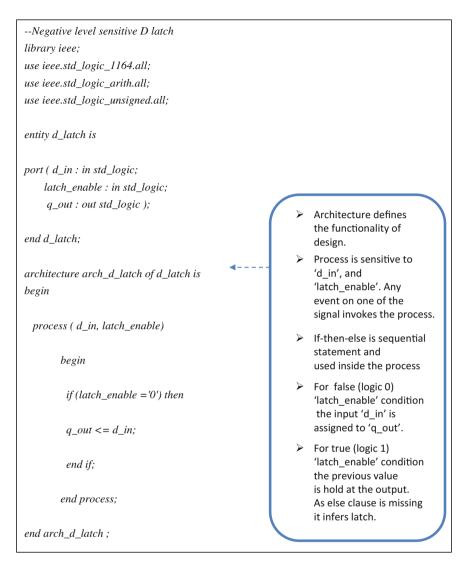

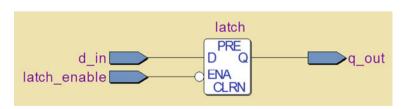

|   |            | 5.2.2    | Negative Level Sensitive D-Latch                   | 132        |

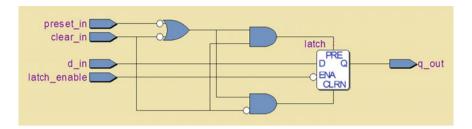

|   |            | 5.2.3    | Negative Level Sensitive D-Latch with Preset       | 125        |

|   |            | 524      | and Clear.                                         | 135        |

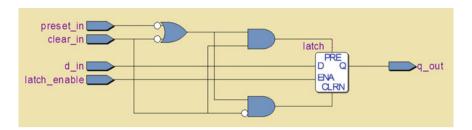

|   |            | 5.2.4    | Positive Level Sensitive D-Latch with Asynchronous | 125        |

|   | <i>5</i> 2 | Elia El  | Preset and Clear                                   | 135        |

|   | 5.3        | -        | lop                                                | 137        |

|   |            | 5.3.1    | Positive Edge-Triggered D Flip-Flop.               | 137        |

|   | <i>5</i> 4 | 5.3.2    | Negative Edge-Triggered D Flip-Flop                | 139        |

|   | 5.4        | •        | ronous and Asynchronous Reset                      | 140        |

|   |            | 5.4.1    | D Flip-Flop with Asynchronous Reset                |            |

|   | ~ ~        | 5.4.2    | D Flip-Flop with Synchronous Reset                 | 142        |

|   | 5.5        |          | ntial Circuit Timing                               | 144        |

|   | 5.6        | -        | ronous Counters                                    | 145        |

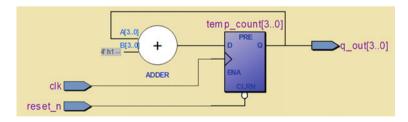

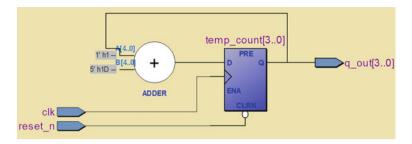

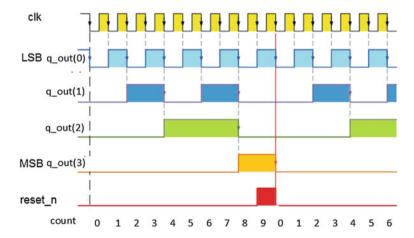

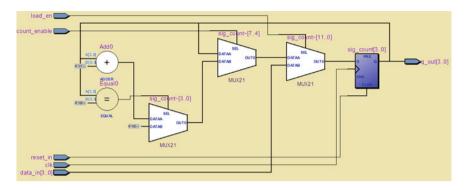

|   |            | 5.6.1    | Four-Bit Up Counter                                | 146        |

|   |            | 5.6.2    | Four-Bit Down Counter                              | 147        |

|   |            | 5.6.3    | BCD Up Counter.                                    | 149        |

|   |            | 5.6.4    | BCD Down Counter                                   | 151        |

|   |            | 5.6.5    | BCD Up-Down Counter                                | 153        |

xiv Contents

| 5.7   | Gray Counter                                                                                                               | 155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.8   | Ring Counter                                                                                                               | 158                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

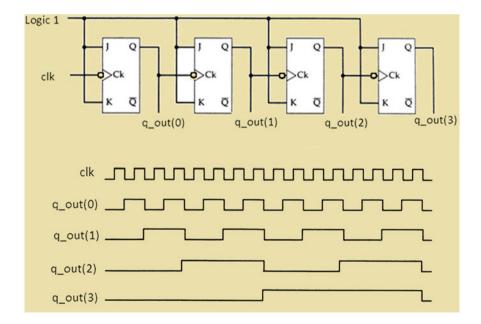

| 5.9   | Johnson Counter                                                                                                            | 159                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

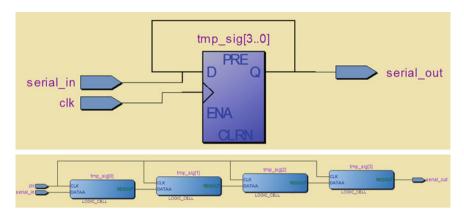

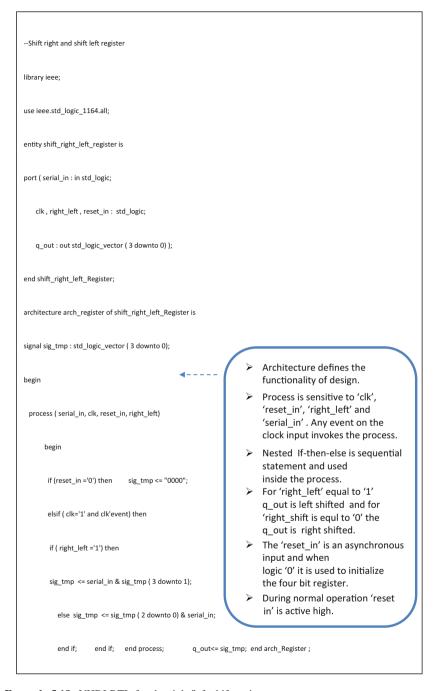

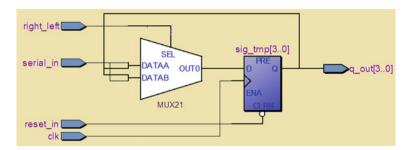

| 5.10  | Shift Registers                                                                                                            | 161                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 5.10.1 Right and Left Shift Registers                                                                                      | 163                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

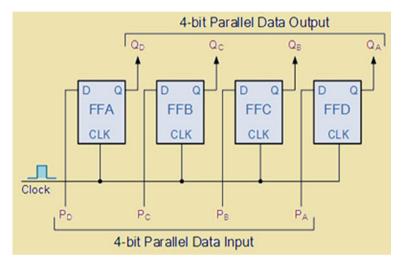

|       | 5.10.2 Parallel Input, Parallel Output (PIPO)                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | Shift Register                                                                                                             | 163                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.11  | Asynchronous Designs                                                                                                       | 167                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.12  | Summary                                                                                                                    | 167                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Intro | duction to PLD                                                                                                             | 169                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.1   | History and Evolution of PLDs                                                                                              | 170                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

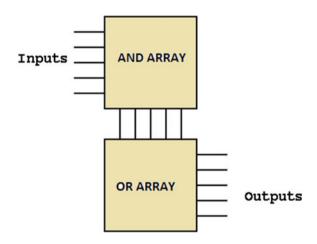

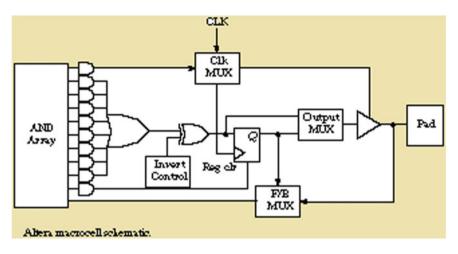

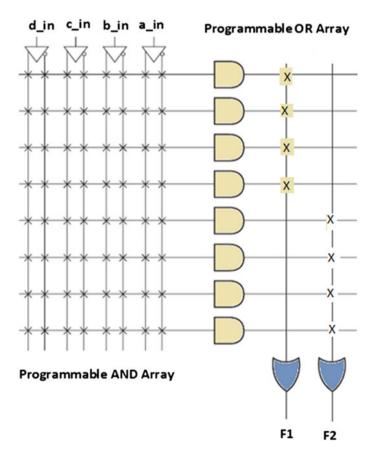

| 6.2   | Simple Programmable Logic Device (SPLD)                                                                                    | 172                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

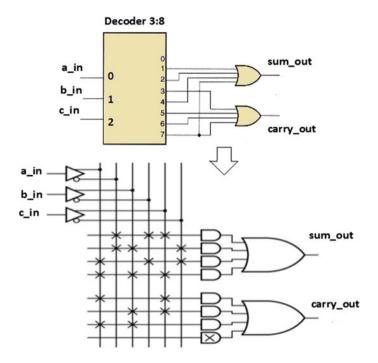

|       | 6.2.1 Programmable Read-Only Memory (PROM)                                                                                 | 174                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

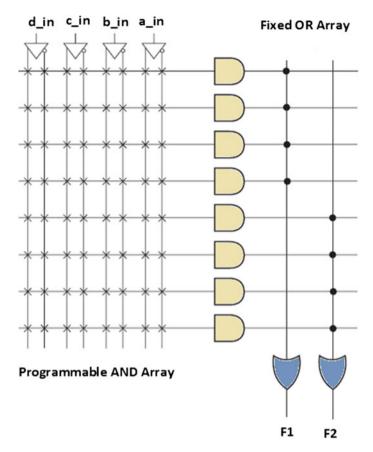

|       | 6.2.2 Programmable Array Logic (PAL)                                                                                       | 175                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

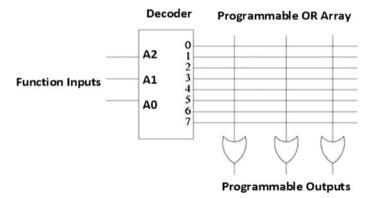

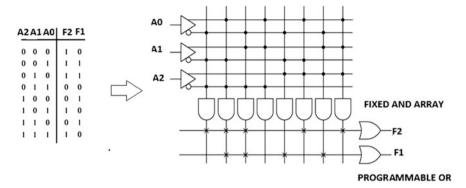

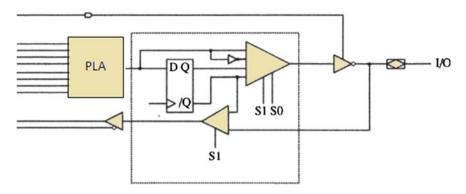

|       | 6.2.3 Programmable Logic Array (PLA)                                                                                       | 175                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

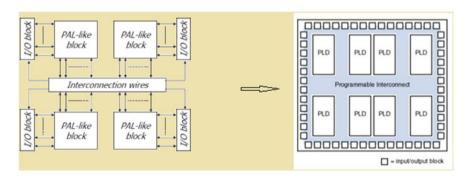

| 6.3   |                                                                                                                            | 178                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

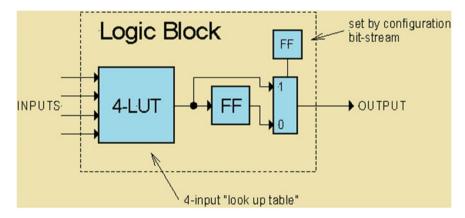

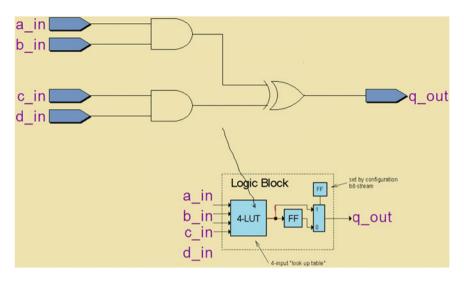

| 6.4   |                                                                                                                            | 181                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

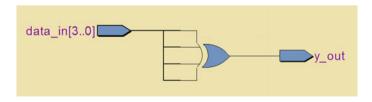

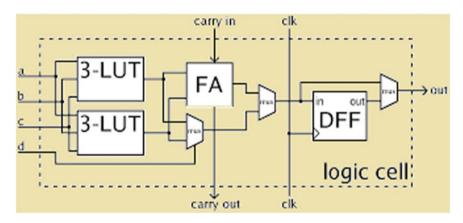

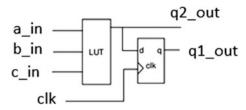

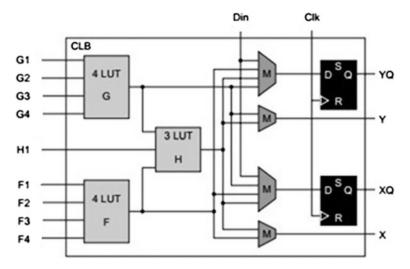

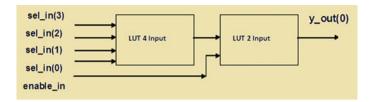

|       | 6.4.1 Concept of LUT and Combinational Logic                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | Realization                                                                                                                | 182                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

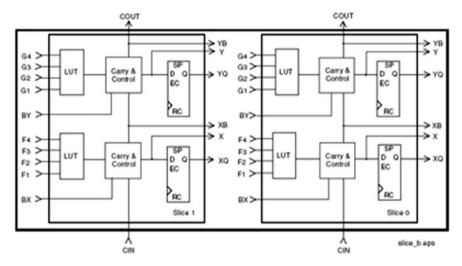

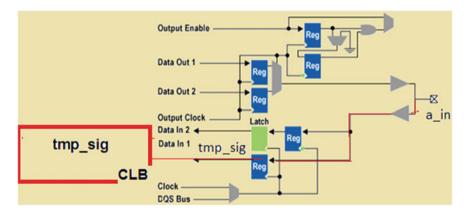

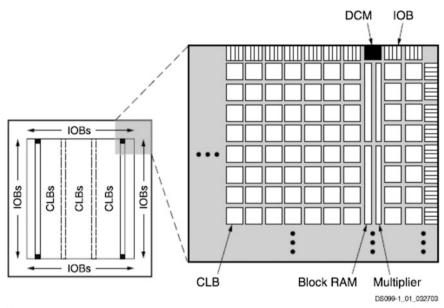

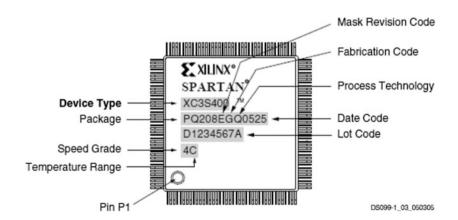

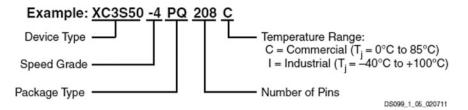

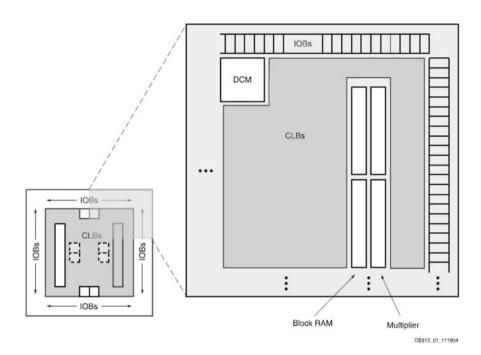

|       |                                                                                                                            | 183                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

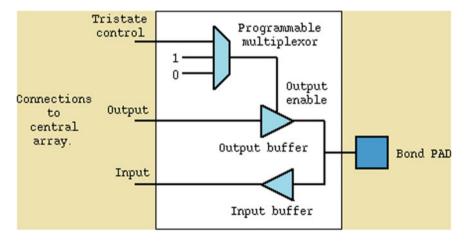

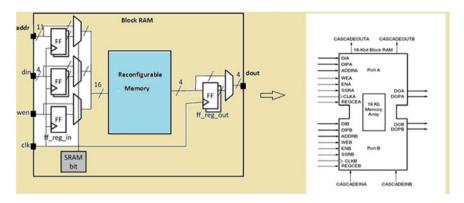

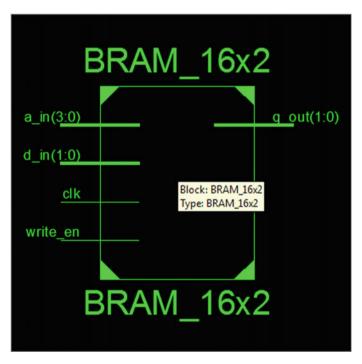

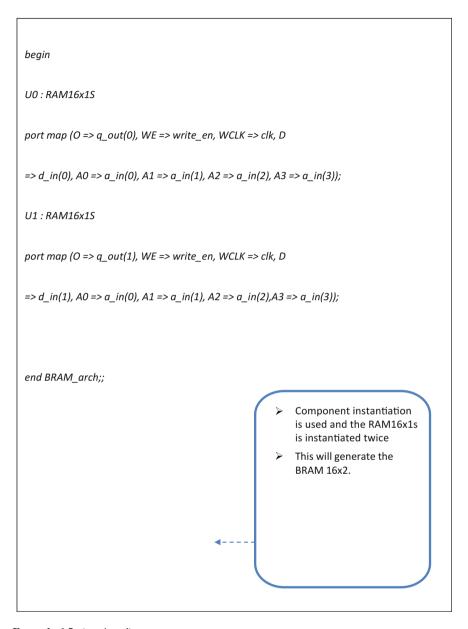

|       |                                                                                                                            | 189                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

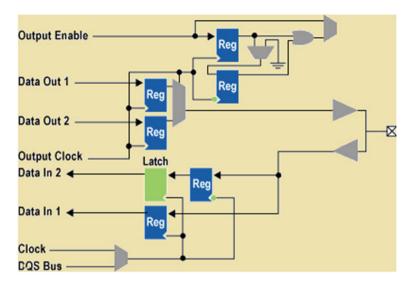

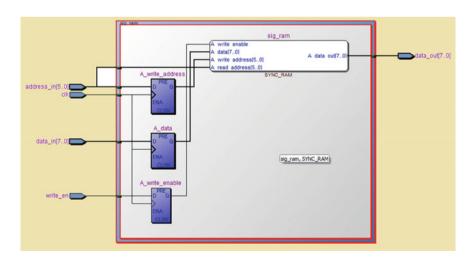

|       |                                                                                                                            | 190                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       |                                                                                                                            | 196                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

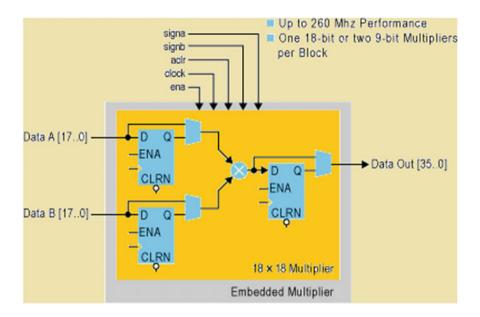

|       |                                                                                                                            | 198                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

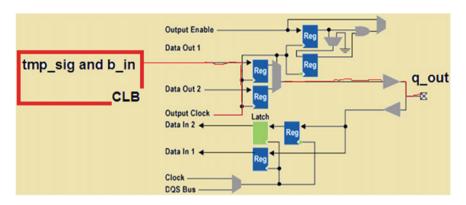

|       |                                                                                                                            | 199                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.5   | Practical Scenarios and Guidelines                                                                                         | 202                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

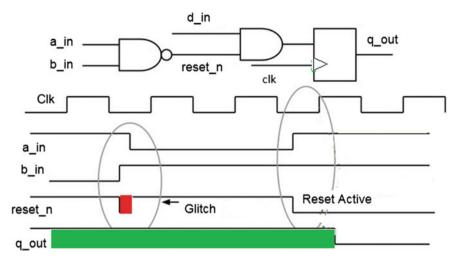

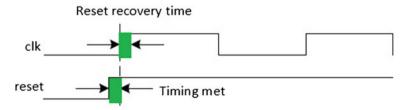

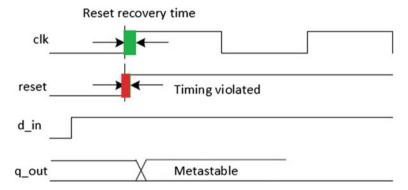

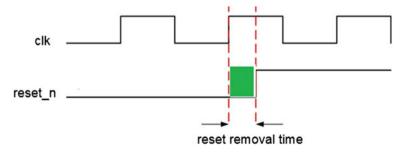

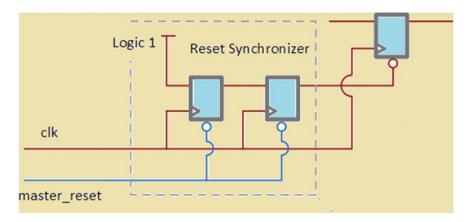

|       | 6.5.1 Reset Strategy                                                                                                       | 202                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 6.5.2 Asynchronous Versus Synchronous Designs                                                                              | 206                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

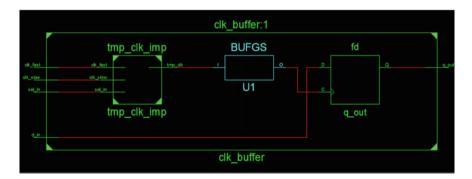

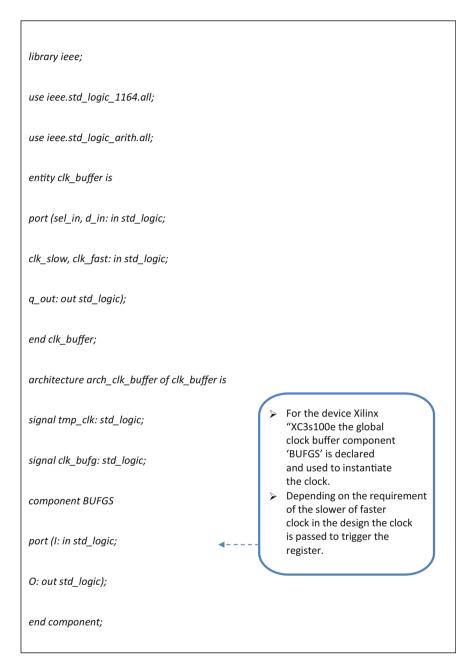

|       | 6.5.3 Clocking Strategies                                                                                                  | 208                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.6   | Summary                                                                                                                    | 209                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Desig | n and Simulation Using VHDL Constructs                                                                                     | 211                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.1   | Simulation Using VHDL                                                                                                      | 212                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

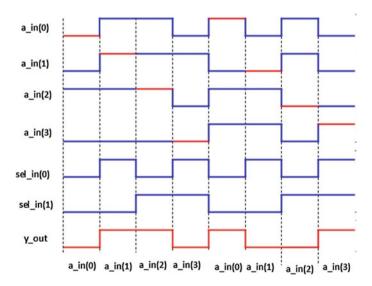

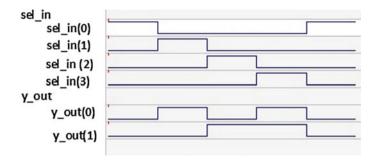

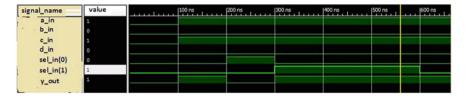

|       | 7.1.1 Testbench for 4:1 MUX                                                                                                | 212                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

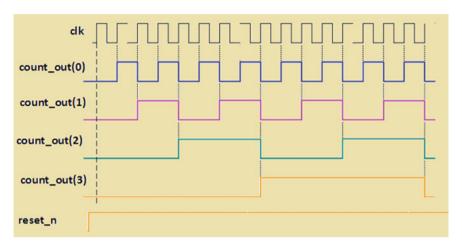

|       | 7.1.2 Testbench for 4-Bit Binary up Counter                                                                                | 215                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.2   | Functions                                                                                                                  | 215                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.3   | Packages                                                                                                                   | 222                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 7.3.1 Package Use in Design                                                                                                | 223                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.4   | Attributes                                                                                                                 | 227                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 7.4.1 Signal Attribute                                                                                                     | 227                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 7.4.2 Array Attribute                                                                                                      | 228                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.5   | File Handling                                                                                                              | 228                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 7.5.1 Use of Files in Design Simulation                                                                                    | 228                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       |                                                                                                                            | 230                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 7.5.2 IEMITO                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | 5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>Intro<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>Desig<br>7.1<br>7.2<br>7.3<br>7.4 | 5.8 Ring Counter 5.9 Johnson Counter 5.10 Shift Registers 5.10.1 Right and Left Shift Registers 5.10.2 Parallel Input, Parallel Output (PIPO) Shift Register. 5.11 Asynchronous Designs 5.12 Summary  Introduction to PLD 6.1 History and Evolution of PLDs 6.2 Simple Programmable Logic Device (SPLD) 6.2.1 Programmable Read-Only Memory (PROM) 6.2.2 Programmable Array Logic (PAL) 6.2.3 Programmable Logic Devices 6.4 Field-Programmable Gate Arrays 6.4.1 Concept of LUT and Combinational Logic Realization. 6.4.2 VHDL Design and Realization Using CLB. 6.4.3 IO Block 6.4.4 Block RAM (BRAM) 6.4.5 Clocking Resources 6.4.6 DSP Blocks and Multipliers 6.4.7 Routing Resources and IO Standards. 6.5 Practical Scenarios and Guidelines 6.5.1 Reset Strategy 6.5.2 Asynchronous Versus Synchronous Designs 6.5.3 Clocking Strategies 6.6 Summary  Design and Simulation Using VHDL Constructs 7.1 Simulation Using VHDL 7.1.1 Testbench for 4:1 MUX 7.1.2 Testbench for 4-Bit Binary up Counter 7.2 Functions 7.3 Packages 7.3.1 Package Use in Design 7.4 Attributes 7.4.1 Signal Attribute 7.4.2 Array Attribute 7.5 File Handling |

Contents xv

| 8 | PLD-       | -Based Design Guidelines                          | 235 |

|---|------------|---------------------------------------------------|-----|

|   | 8.1        | Naming Conventions                                | 236 |

|   | 8.2        | Use of Signals and Variables                      | 236 |

|   | 8.3        | Grouping in Design                                | 239 |

|   | 8.4        | Guidelines for Use of Tri-State Logic             | 240 |

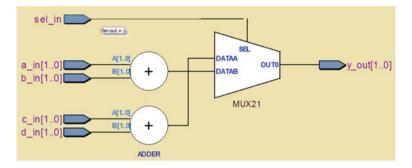

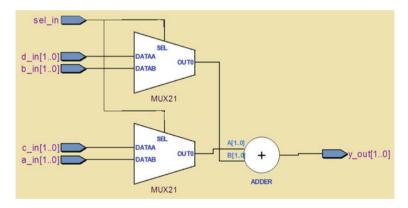

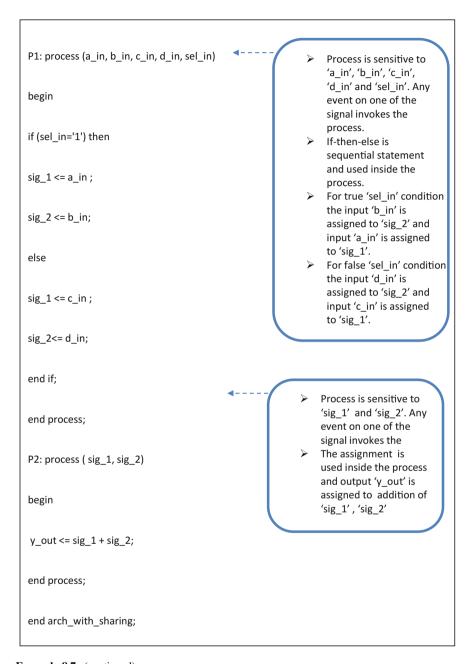

|   | 8.5        | Arithmetic Resource Sharing                       | 243 |

|   | 8.6        | Logic Duplications                                | 245 |

|   | 8.7        | Multiple Driver Assignments                       | 248 |

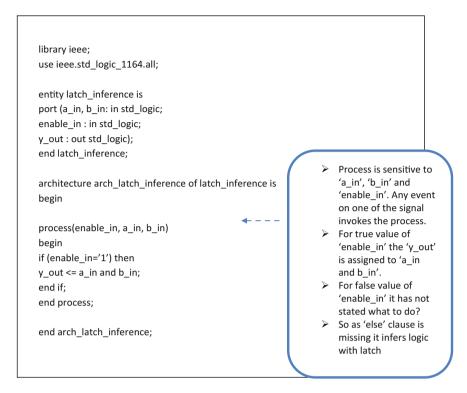

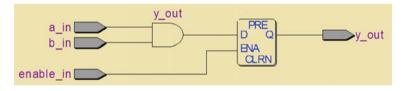

|   | 8.8        | Inferring Latches                                 | 254 |

|   | 8.9        | Use of If Then Else Versus Case Statements        | 255 |

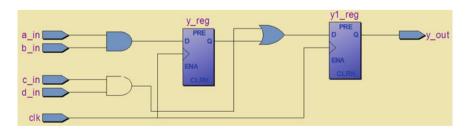

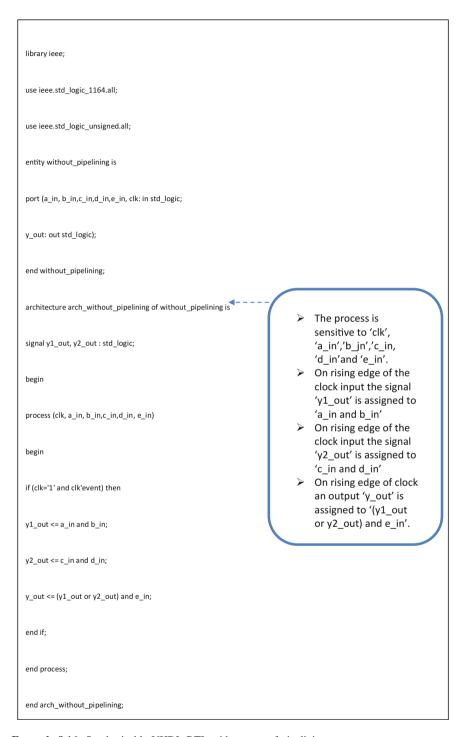

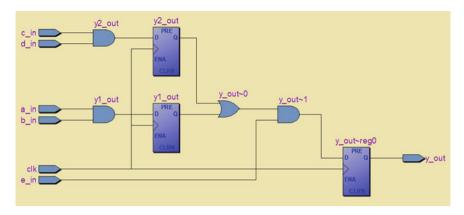

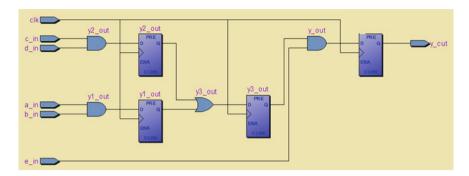

|   | 8.10       | Use of Pipelining in Design                       | 258 |

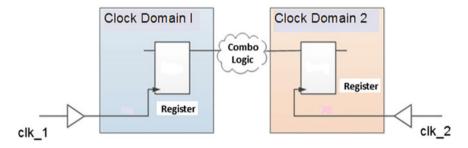

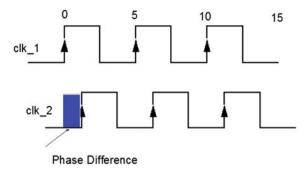

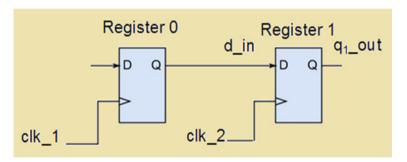

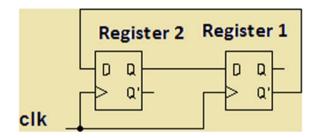

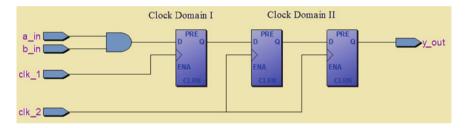

|   | 8.11       | Multiple Clock Domain and Data Passing            | 262 |

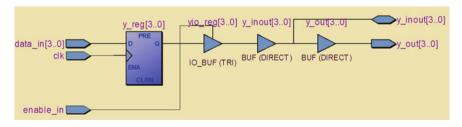

|   | 8.12       | Bidirectional IO                                  | 266 |

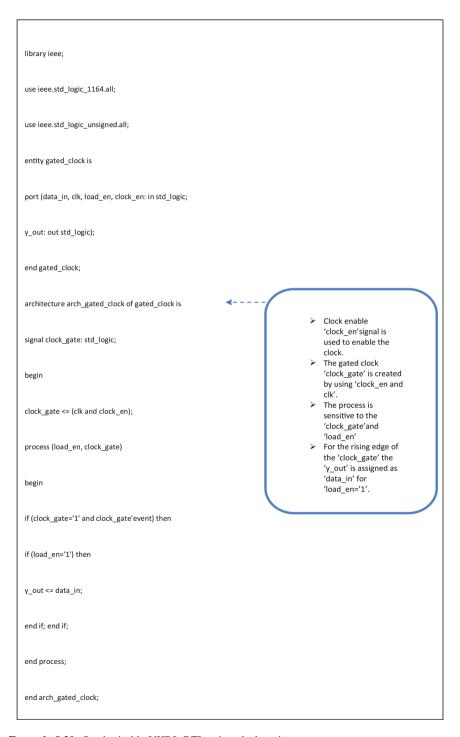

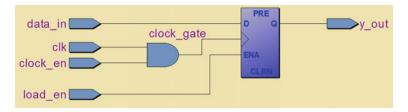

|   | 8.13       | Gated Clock                                       | 269 |

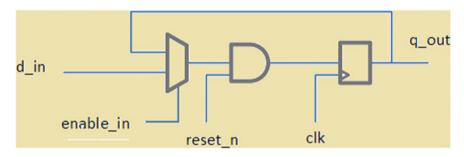

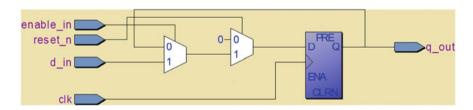

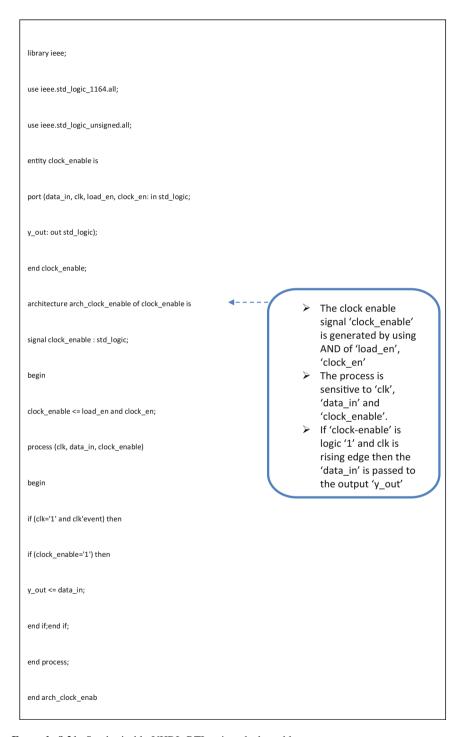

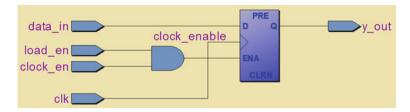

|   | 8.14       | Design with Clock Enable                          | 269 |

|   | 8.15       | Summary                                           | 271 |

| 9 | Finite     | e-State Machines                                  | 273 |

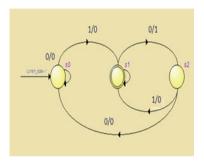

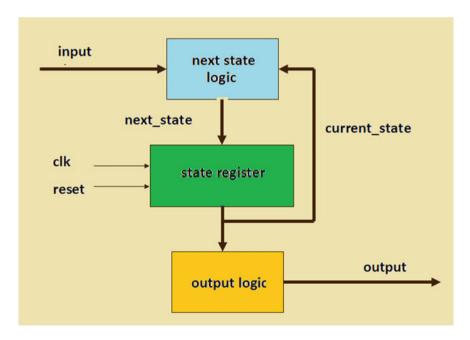

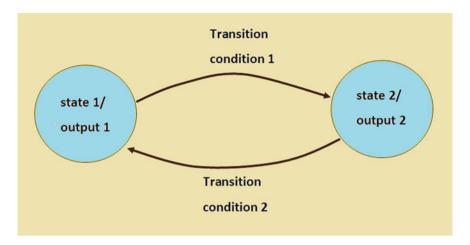

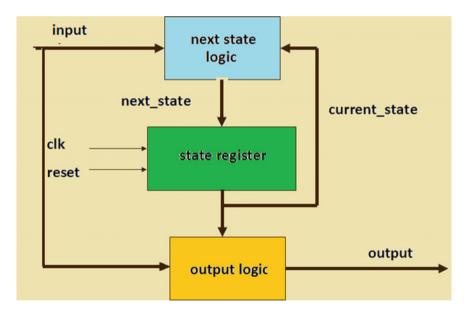

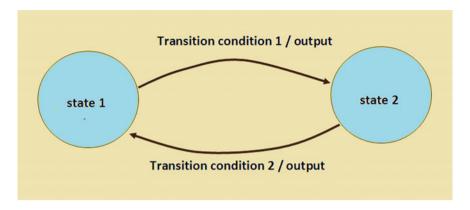

|   | 9.1        | Introduction to FSM                               | 273 |

|   | <b>7.1</b> | 9.1.1 Moore Machine                               | 274 |

|   |            | 9.1.2 Mealy Machine                               | 275 |

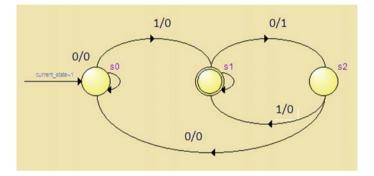

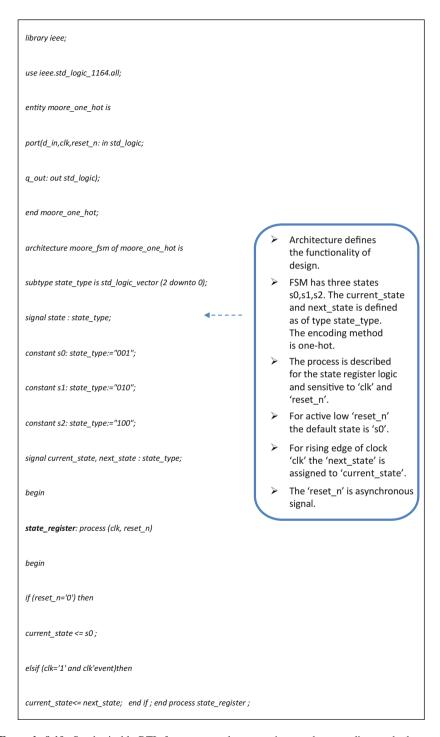

|   | 9.2        | FSM Encoding Methods.                             | 277 |

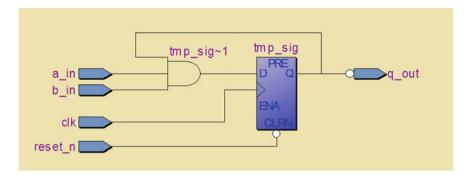

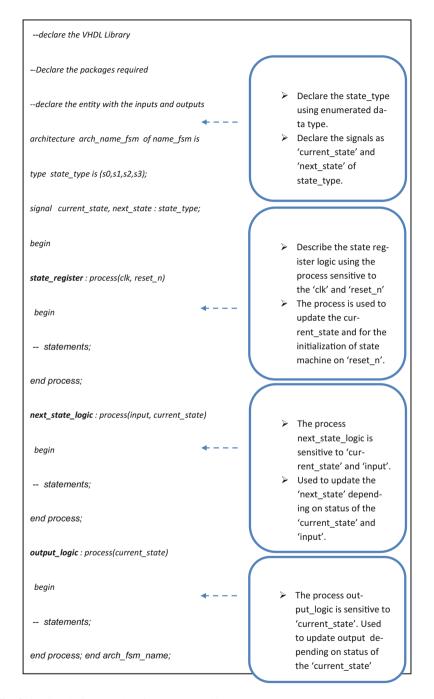

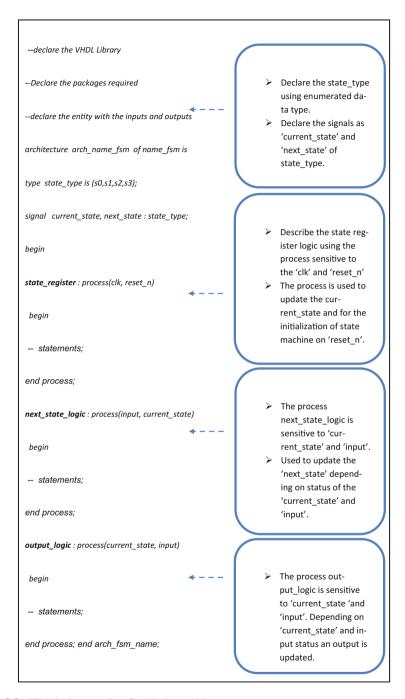

|   | 9.3        | How to Code Moore FSM Using VHDL?                 | 279 |

|   | , ,,       | 9.3.1 FSM Design Template for Moore Machine       | 281 |

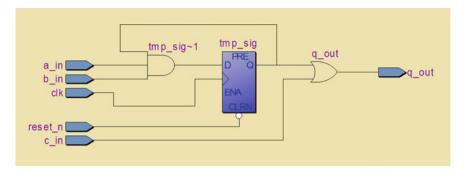

|   | 9.4        | How to Code Mealy FSM Using VHDL?                 | 281 |

|   |            | 9.4.1 FSM Design Template for Mealy Machine       | 283 |

|   | 9.5        | FSM Examples and VHDL Coding                      | 283 |

|   |            | 9.5.1 Binary Encoding FSM                         | 286 |

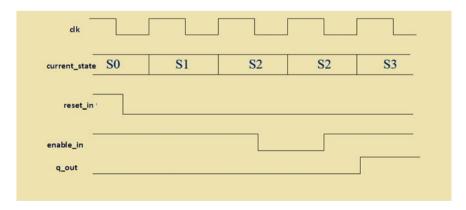

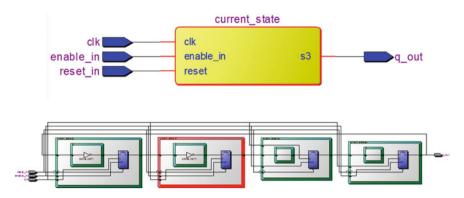

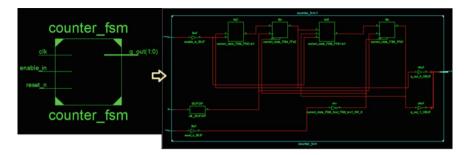

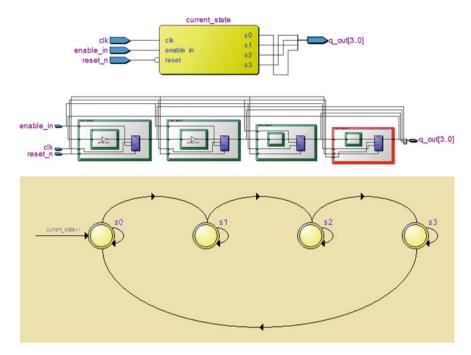

|   |            | 9.5.2 Binary Counter FSM                          | 289 |

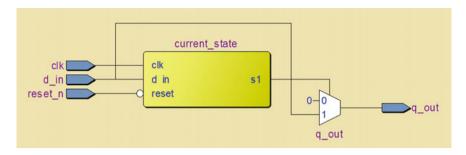

|   |            | 9.5.3 One-Hot Counter FSM                         | 289 |

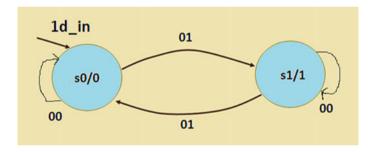

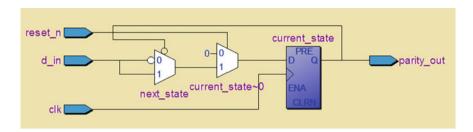

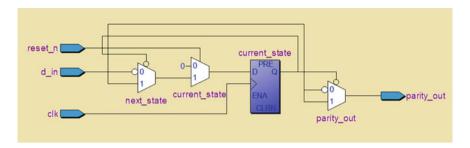

|   | 9.6        | Parity Logic Using Moore FSM                      | 289 |

|   |            | 9.6.1 Moore Machine: Three-Process Block FSM      |     |

|   |            | for Parity Checking                               | 292 |

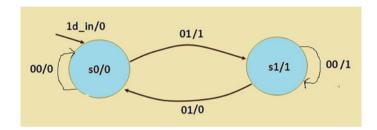

|   | 9.7        | Parity Logic Using Mealy FSM                      | 292 |

|   |            | 9.7.1 Mealy Machine: Two-Process Block FSM        |     |

|   |            | for Parity Checking                               | 298 |

|   |            | 9.7.2 Mealy Machine: Three-Process Block FSM      |     |

|   |            | for Parity Checker                                | 298 |

|   | 9.8        | Sequence Detector Mealy Machine                   | 303 |

|   | 9.9        | One-Hot Encoding Sequence Detector: Moore Machine | 306 |

|   | 9.10       | One-Hot Encoding Sequence Detector: Mealy Machine | 306 |

|   | 9.11       | FSM Optimization                                  | 308 |

|   | 9.12       | Summary                                           | 312 |

xvi Contents

| 10 | Synth | hesis Optimization Using VHDL                        | 313 |

|----|-------|------------------------------------------------------|-----|

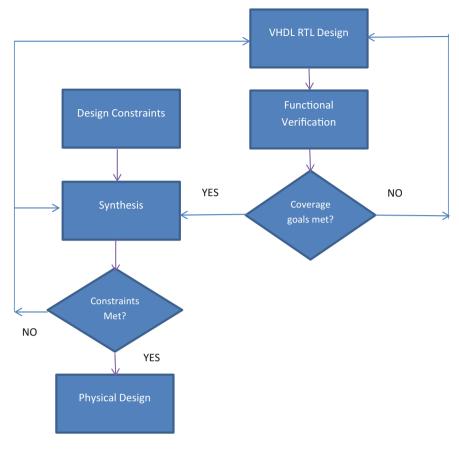

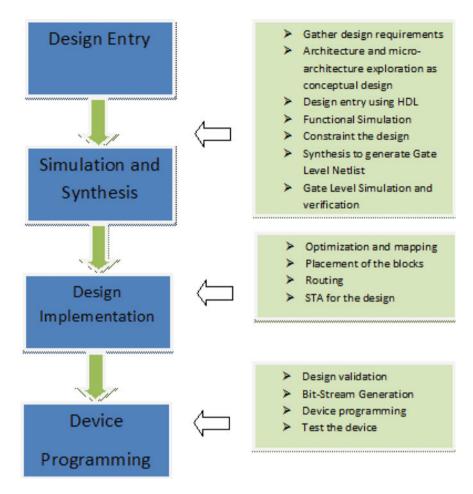

|    | 10.1  | FPGA Design Flow                                     | 314 |

|    |       | 10.1.1 Design Entry                                  | 314 |